AI开发-效率提升小工具-“打盹弹窗侠”记录

自从不再上班,工作起来常常忘我,有时连午休都忘记了,虽然很享受这种投入的状态,但是不休息会导致下午效率不高,我用AI快速写了一个小工具,每天12点来一次霸屏提示。

🚀 午休提醒神器 — 让休息不再忘记!

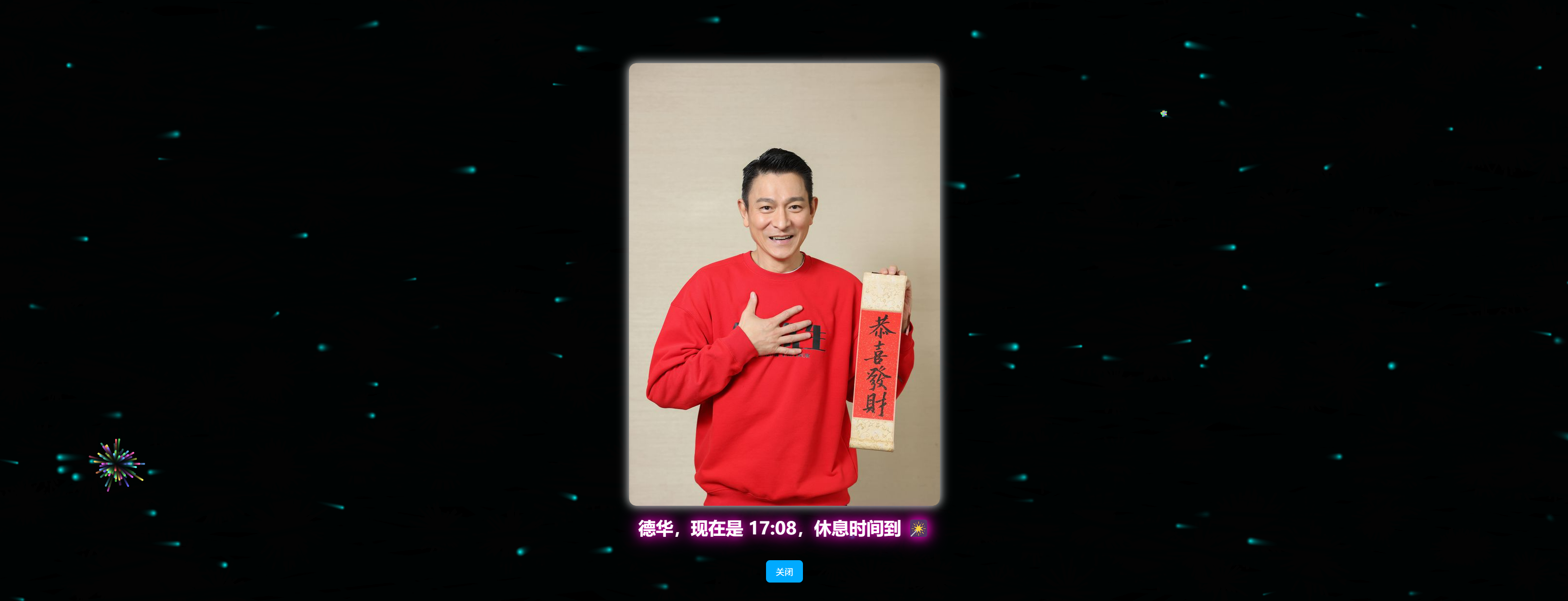

💥 酷炫全屏弹窗,自动提醒你休息时间,配上流畅的粒子动画和烟花效果,告别沉迷工作,给你最温暖的提醒。

🎯 核心功能:

- 自动化:通过 Windows 计划任务定时弹出提醒

- 全屏效果:强制休息,将所有当前打开的窗口最小化,清晰、直观、无法忽视

- 炫酷动画:粒子碰撞烟花,休息时间更有仪式感

- 高度定制:背景图片、时间提示,轻松换

💡 适用场景:

- 午休提醒:每天准时提醒,告别疲劳

- 眼保健操/久坐提醒:定时休息,保护视力

- 家庭作息管理:也可以用来帮助孩子养成良好习惯

下面是我和AI对话的提示词总结,结构清晰、简洁易懂,方便其他人复刻并定制这个项目:

💡 项目目标:

创建一个Chrome全屏弹窗提醒工具,用于午休提醒,支持炫酷动画背景、显示时间、图片和“关闭”按钮。

✅ 功能清单:

- 打开 Chrome App 模式窗口显示本地 HTML 页面

- 打开前自动隐藏所有窗口(类似“显示桌面”)

- 移动 Chrome 窗口到指定屏幕并全屏

- 页面包含:提示时间、图片、按钮

- 页面背景带有:炫酷粒子动画 + 粒子相撞烟花效果

- 粒子从左右同时飞入,相撞时按体积爆炸烟花,大小动态

🧾 提示词模板(Prompt):

帮我实现一个午休提醒工具,需求如下:1. 使用 Windows 批处理脚本和 AutoHotKey 脚本:- 打开前最小化或隐藏所有窗口(效果如“显示桌面”)- 启动 Chrome 并打开一个本地 HTML 页面(使用 App 模式)- 启动后移动窗口到指定屏幕并全屏显示2. HTML 页面内容:- 黑色背景- 居中显示一张图片- 上方显示当前时间的文字提示,例如“现在是 14:30,休息时间到”- 下方一个“关闭”按钮,点击关闭窗口3. 页面动画效果:- 使用 `<canvas>` 实现动态背景- 显示炫酷粒子从左右两侧同时飞入- 粒子相撞后产生烟花爆炸特效- 粒子大小影响爆炸大小,小粒子产生小爆炸- 所有动画铺满整个背景,不局限于页面左侧请给我 HTML 页面完整代码,同时也需要提供启动脚本和 AHK 脚本。

🧰 所用技术:

- HTML + CSS + JS (粒子动画 + canvas 烟花特效)

- 批处理脚本

.bat(打开 Chrome,延时,调用 AHK) - AutoHotKey 脚本

.ahk(隐藏所有窗口,移动并全屏 Chrome)

🚀 项目文件结构建议:

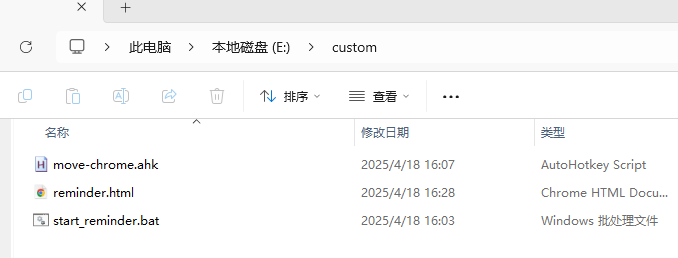

customer/

├── reminder.html # 主页面(含粒子动画和烟花)

├── start_reminder.bat # 启动脚本(打开浏览器)

├── move-chrome.ahk # AHK 脚本(控制窗口位置)

共三个文件:

需要我也一并整理出 .bat 和 .ahk 的最终版本吗?可以让整个项目即拷即用。