最近有好几个星球会员问到物理验证Calibre LVS检查中的Stamping Conflict问题。小编今天给大家分享下Stamping冲突的相关topic。

Calibre PEX Hspice Netlist提取步骤(数模芯片提取spice netlist流程)

Stamping Conflict概念

当不同的net对应的net shape连接到同一条net上,此时Calibre LVS检查就会报Stamping Conflict。而且这个连接关系是通过LVS Deck文件中SCONNECT定义的。比如N+连接到NWELL,P+连接到PSUB。

所以这是一个soft connect。net的信息是从高层往低层传递的(单向连接关系)。这里以下图所示的两个NMOS为例,左边的NMOS管的P+是连接到Digital GND,而右侧的NMOS的P+是连接到模拟地AGND。此时工具就会从高层的PG Text把对应的net信息传递给P+,而且工具发现存在两条不同的net都连接到P+,这时候就会报Stamping Conflict冲突。

所以在咱们社区T12nm A55后端训练营项目中做PG连接性检查时需要带上noSoftPGConnect选项。

Calibre LVS -手把手教你如何debug LVS的short和open

verifyConnectivity -type special -noAntenna -noWeakConnect -noUnroutedNet -error 100000 -warning 50 -net VDD_CORE -noSoftPGConnect

而且右侧那个NMOS必须就近要能找到这么一个P+的tap接触,否则就会有Latchup效应。

Stamping Conflict原因

1)PG Open/Floating情况

下图所谓为一个典型VSS Power Rail Floating的情况。Calibre LVS在做GDS抽取过程会报Extraction的警告!该警告会提示:“Net VSS is selected for stamping” 。而且会告知我们哪一条net被拒绝Rejected。

通过Calibre RVE我们可以很快高亮被rejected的net 1469,快速找出pg floating的点。下图所示为一个design的power ring挡住了高层PG Stripe和power rail M1打孔的案例。

这里重点提醒下:设计中有soft connect问题必须解决。而ERC的有些错误可能是假的,但这种一般都是设计中两条不同的信号short在一起了(或missing label)。

又比如下面这个设计版图,M1没有完整连接上,此时Calibre LVS也会报stamping conflict冲突,上面那条net被工具rejected掉。虽然最终的LVS也能过,但是LVS的抽取报告必须清干净!

2)多个ground连接到同一个PSUB

下设计所示为两个不同的Ground同时连接到同一个PSUB,这两个Ground分别是VSS_DIG和VSS_ANA。

此时如果拿这个的设计去做LVS检查,我们也会看到上图所示的Stamping冲突。如果去看GDS的抽取netlist,我们也可以看到PSUB被工具认成是连接到VSS_DIG。而设计的本意是这两个管子的PSUB是不一样的,因此最终Calibre LVS是过不了的。

正确的spice netlist应该是如下图所示的连接关系。遇到这种case,我们就需要给不同的区域画上PSUB2层。

LVS文件中,我们经常遇到PSUB2或者SUBD这样的layer定义,这个特殊的layer是干什么用的,我们如何利用好它的定义呢?

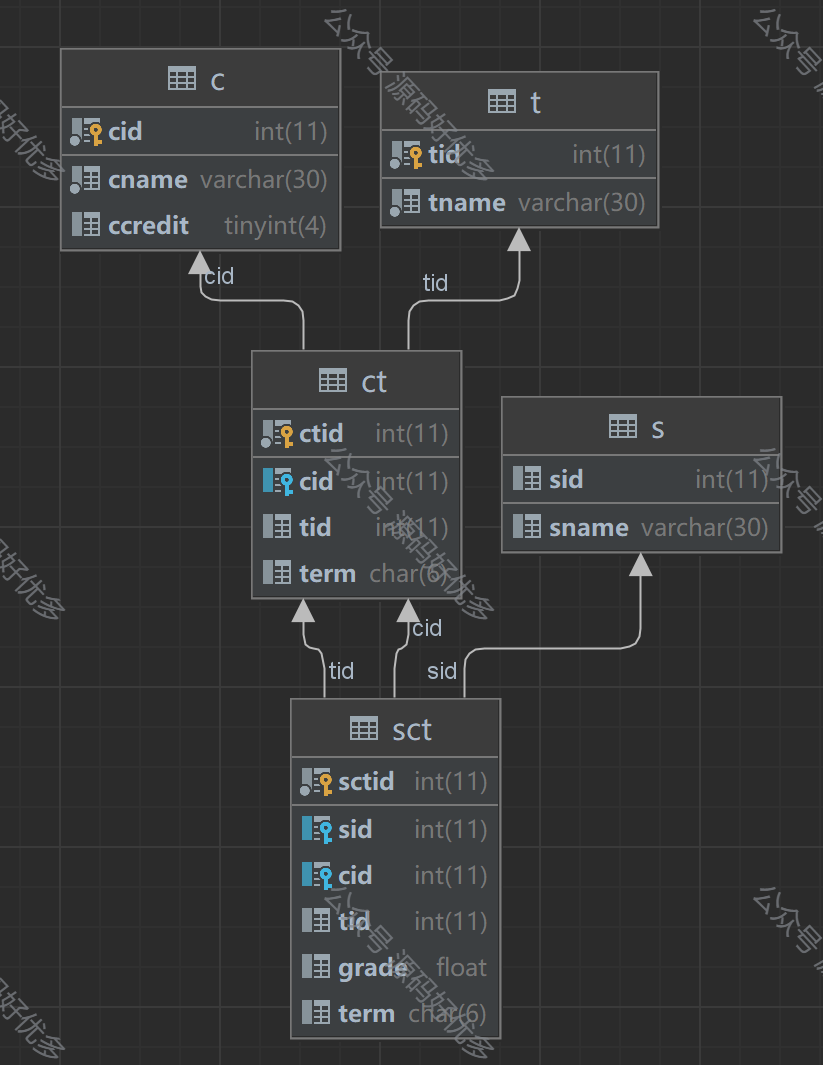

下图是通过pcell自动生成4个nmos管的layout。

下图是通过pcell自动生成4个nmos管的cdl网表:

我们本来期望它做LVS是CORRECT的,但是运行后,却报错如下:CELL COMPARISONRESULTS ( TOP LEVEL )

Error: Different numbers of nets

Error: Connectivity errors.

NUMBERS OF AFTER OBJECTS

Layout Source ------ ------

Ports: 0 0

Nets: 13 16

Instances: 4 4

Total Inst: 4 4

通过上述报错可以分析出:错误的原因在于Net的个数不对,在cdl端有16个net,而在layout端只有13个net,二者出现了差距。

cdl端的16个net符合我们预期,一共有4个mos管,每个mos管有4个terminal,合计有16个net,这个是对的。

layout端的13个net的原因是:4个nmos管的衬底端本来希望都不是一个节点,结果在版图中都连接成了一个节点,这样4个衬底节点少了3个,就出现了Incorrect。由于nmos管的衬底是pwell,4个nmos管的衬底默认都是连接在一起的,因此,就出现了与cdl不一致的问题。

那应该如何解决这种LVS问题呢?

在每个nmos管外面都覆盖了一个粉红色的PSUB2的layer,它的作用就是:使得4个nmos管的衬底从原来的1个节点变为4个节点,具体如下图所示。

所以PSUB2的作用就是起隔离作用,它自动把该图形的区域与其它区域的节点分割成2个不同的节点。在SoC数模混合芯片中会频繁通过添加PSUB2层来隔离不同的PSUB(数字地VSS和各种模拟地AVSS)。

3)Sealring/GuardRing Floating Tap

下图所示为悬空Tap导致的stamping冲突。此时也是相当于两条不一样的net接到PSUB。

解决办法也很简单——只需要把悬空的Tap用M1和M1的VSS连成一片即可解决。

[思考题] 如下a7top物理验证calibre LVS结果有问题可能的原因有哪些?