摘要:本文章主要描述如何自动化将IC code通过synplify生成edf文件后,转入Vivado进行Link design,然后生成dcp文件。本文章仅仅是记录本人的整体实现思想。

一、背景以及整体流程介绍

由于IC code全部放在服务器A,vivado在服务器B;所以会有一些额外的操作:

1. 先进入服务器A,git pull ic code

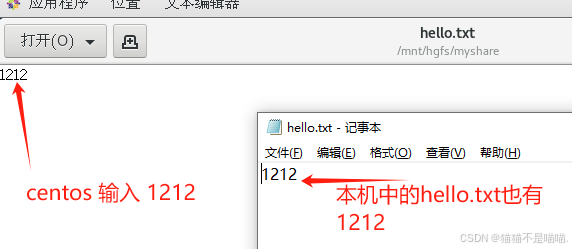

通过服务器B访问A的时候需要做免密操作。

2. 找到需要的Filelist

一般ic designer需要提供fpga版本的filelist,必须和FPGA原型验证相关人员统-filelist格式以及filelist的命名规则;

3.根据filelist生成synplify能够运行的“.prj”文件

一般synplify通过图形化界面生成project的时候会生成脚本prj文件。可以根据这个文件完成py脚本;

4.cd到步骤3的“.prj”文件路径下执行synplify

synplify_pro -batch *.prj&& echo'successfully' echo 'failed

5.cd到步骤3的“.prj”文件路径下执行synplify

6.synplify执行完成之后会生成edf文件,找到edf路径文件

7.生成好需要用到的xilinxip,并指定路径

例如:xilinx phy、xilinx ram ip、xilinx dsp

8.生成vivado所需要的tcl文件并souce

需要注意link design

AMD Technical Information Portal

AMD Customer Community

AMD Customer Community

AMD Technical Information Portal

此步骤最后会生成dcp文件(当成ip使用)

# 远程服务器信息

remote_user="yuyushan"

remote_host="10.0.0.103"ssh $remote_user@$remote_host "bash /home/users/yuyushan/yuyushan_97/python/edf103_2_dcp97/iccode2edf_103.sh"cd /data/yuyushan_97/python/edf103_2_dcp97 || exit 1# 读取文件中的目录路径

directory_path=$(cat /data/yuyushan_97/python/edf103_2_dcp97/gen_syn_prj_path.txt)

last_part=$(basename "$directory_path")

second_last_part=$(dirname "$directory_path" | xargs basename)edf_dir_path="/data/yuyushan_97/$second_last_part/$last_part"

# echo "$edf_dir_path/rev1"python3 /data/yuyushan_97/python/edf103_2_dcp97/gen_link_design_tcl.py $edf_dir_path/rev_1cd /data/yuyushan_97/link_synplify_vivado/ || exit 1sleep 3spwdvivado -mode tcl -source *.tclsleep 5srm -rf *.tclgen_synplify_edf_path="/home/users/yuyushan/yuyushan_97/gen_synplify_edf_103/"rsp_s1_top_filelist_fpga="/prj/chips/pvg/venus/yuyushan/jade_venus_3/vobs/ip/rsp/design/rsp_s1_top/"

rsp_s1_filelist_fpga="/prj/chips/pvg/venus/yuyushan/jade_venus_3/vobs/ip/rsp/design/rsp_s1/"

rsp_transpose="/prj/chips/pvg/venus/yuyushan/jade_venus_3/vobs/ip/rsp/design/rsp_transpose/"

rsp_s3="/prj/chips/pvg/venus/yuyushan/jade_venus_3/vobs/ip/rsp/design/rsp_s3/"

rsp_top="/prj/chips/pvg/venus/yuyushan/jade_venus_3/vobs/ip/rsp/design/rsp_top/"file_list=$rsp_s1_top_filelist_fpgasub="/prj/chips/pvg/venus/yuyushan/jade_venus_3/vobs/ip/rsp/design/rsp_s1/sub"

vobs="/prj/chips/pvg/venus/yuyushan/jade_venus_3/vobs"

input_synplify_folder_path="/home/users/yuyushan/yuyushan_97/gen_synplify_edf_103/"cd $vobs

git pull

cd $sub

git pull# 本地 Python 脚本信息

gen_synplify_project="/home/users/yuyushan/yuyushan_97/python/edf103_2_dcp97/gen_synplify_project.py"#使用python生成路径

python3 $gen_synplify_project $file_list $input_synplify_folder_path > /home/users/yuyushan/yuyushan_97/python/edf103_2_dcp97/gen_syn_prj_path.txt# 读取文件中的目录路径

directory_path=$(cat /home/users/yuyushan/yuyushan_97/python/edf103_2_dcp97/gen_syn_prj_path.txt)

echo $directory_path# 切换到目录

cd "$directory_path" || exit 1########################synplify_pro *.prj &sleep 5spwdsynplify_pro -batch *.prj && echo 'successfully' || echo 'failed'sleep 5s具体python代码和脚本代码不会在文章中体现。