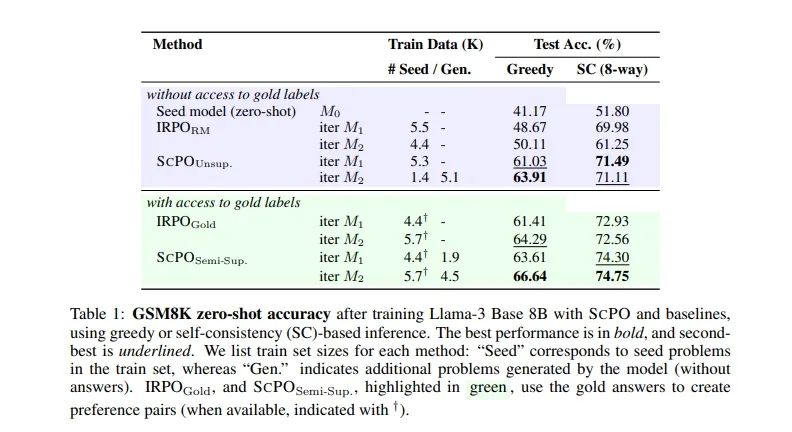

数字IC实践项目(10)—基于System Verilog的DDR4 Model/Tb 及基础Verification IP的设计与验证(付费项目)

- 前言

- 项目框图

- 1)DDR4 Verification IP

- 2)DDR4 JEDEC Model & Tb

- 项目文件

- 1)DDR4 Verification IP

- 2)DDR4 JEDEC Model & Tb

- Wave&Coverage

- 1)DDR4 Verification IP

- 2)DDR4 JEDEC Model & Tb

- 3)DDR4 IBIS model sim

- 自动化脚本

- 1)Makefile脚本

- 2)Python自动化脚本

- 项目简介和资料

- 1)项目简介

- 2)拓展资料

- 软件环境要求

- 总结

前言

在之前的博客中,推出的CNN硬件加速器的设计与实现,获得了积极的反馈。这次,我希望可以继续拓展项目,避免项目同质化,帮助更多同学在秋招中提前锁定Offer,借此推出关于DDR4接口协议、仿真模型及验证IP(Verification IP)的全新项目。

对于找工作的帮助:

-

技术能力提升

掌握DDR4协议和相关仿真技术,可以增强在嵌入式系统、数字IC设计和验证领域的专业能力。 -

市场需求匹配

内存接口在市场上有很高的需求,尤其是在AI、视频处理、高速计算和数据中心领域。 -

项目经历展示

该项目可以作为简历中的重要经历,展示个人技术能力和项目管理能力,帮助你在众多求职者中脱颖而出。

项目框图

1)DDR4 Verification IP

DDR4 Verification IP项目框图的结构如下:

-

DIMM_Model:该模块用于模拟DDR4内存模块的行为,主要负责对DIMM(Dual Inline Memory Module)结构及其接口进行建模。它实现了对从DDR_TOP发送的命令的处理,包括读、写和其他控制信号,并返回相应的数据。

-

Random_Stimulus:此模块的主要功能是生成随机的激励信号,以测试DDR4接口的响应能力和稳定性。通过设计多种读写模式和边界条件,Random_Stimulus能够确保全面覆盖随机读写地址及数据操作场景。

-

DDR_TOP:作为项目的核心模块,DDR_TOP负责管理DDR4的状态机,处理各类命令的执行,包括激活(ACT)、写入(WR)、读取(RD)和预充电(PRE)等操作。它依据生成的随机激励,协调命令和数据的发送与接收。同时,DDR_TOP还会严格遵循DDR4规范,避免如空读、单个bank重复激活等违规操作,确保数据传输的准确性和可靠性。

-

MEMORY_CHECK:这一模块负责对内存操作的正确性进行检查,涵盖数据完整性、时序分析及一致性验证等功能。MEMORY_CHECK会监控DDR_TOP的操作结果,确保所有读写操作符合预期,并能够及时捕捉到潜在的错误或不一致之处,为设计提供反馈。

-

DDR_CLOCK:该模块提供DDR4所需的时钟信号,确保数据传输的同步性和稳定性。DDR_CLOCK不仅负责生成基本的时钟信号,还包括时钟延迟和相位调整,从而支持不同工作频率下的性能测试。

-

DDR_VECTOR:DDR_VECTOR模块用于产生Hspice格式激励,可用于实际电路的输入和输出比较,确保电路设计的准确性。

-

DDR Interface:此模块作为DDR4内存与外部系统之间的连接桥梁,负责数据的输入和输出。它确保了数据传输的可靠性,并处理信号转换、时序匹配等问题。

-

TB (Testbench):测试平台将所有模块集成在一起,进行全面的功能验证和性能测试。TB通过Random_Stimulus生成激励信号,监控DDR_TOP的行为,并利用MEMORY_CHECK进行结果的验证。测试平台还可以配置不同的测试场景和参数,以适应各种验证需求,确保DDR4 IP在各种条件下均能正常工作。

2)DDR4 JEDEC Model & Tb

项目额外提供一个标准JEDEC的DDR4 仿真Model及相关Tb,顶层设计如下:

- Timing Setting table:提供1066~4000Mbps,覆盖完整JEDEC Spec速度挡位的相关Timing设定;

- Golden behavior model: 提供JEDEC 标准DDR4的行为模型,支持Act/Write/Read/Pre/MRW/MRR等操作;

- DDR4 interface:提供全局DDR4接口信号,例如CK/DQS/DQ/CA等;

- testbench: 提供顶层测试模块,涵盖Power Up/Power Down/MRW/Refresh/Precharge/Activate/Write/Read等基础操作task;

- Other:提供包含容量、位宽定义等相关项目参数定义。

项目文件

项目文件列表如下:

1)DDR4 Verification IP

2)DDR4 JEDEC Model & Tb

Wave&Coverage

1)DDR4 Verification IP

2KB Random Wr/Rd Stimulus

Memory check report & final rpt

Code Coverage

2)DDR4 JEDEC Model & Tb

tccds seamless wr/rd

Code Coverage

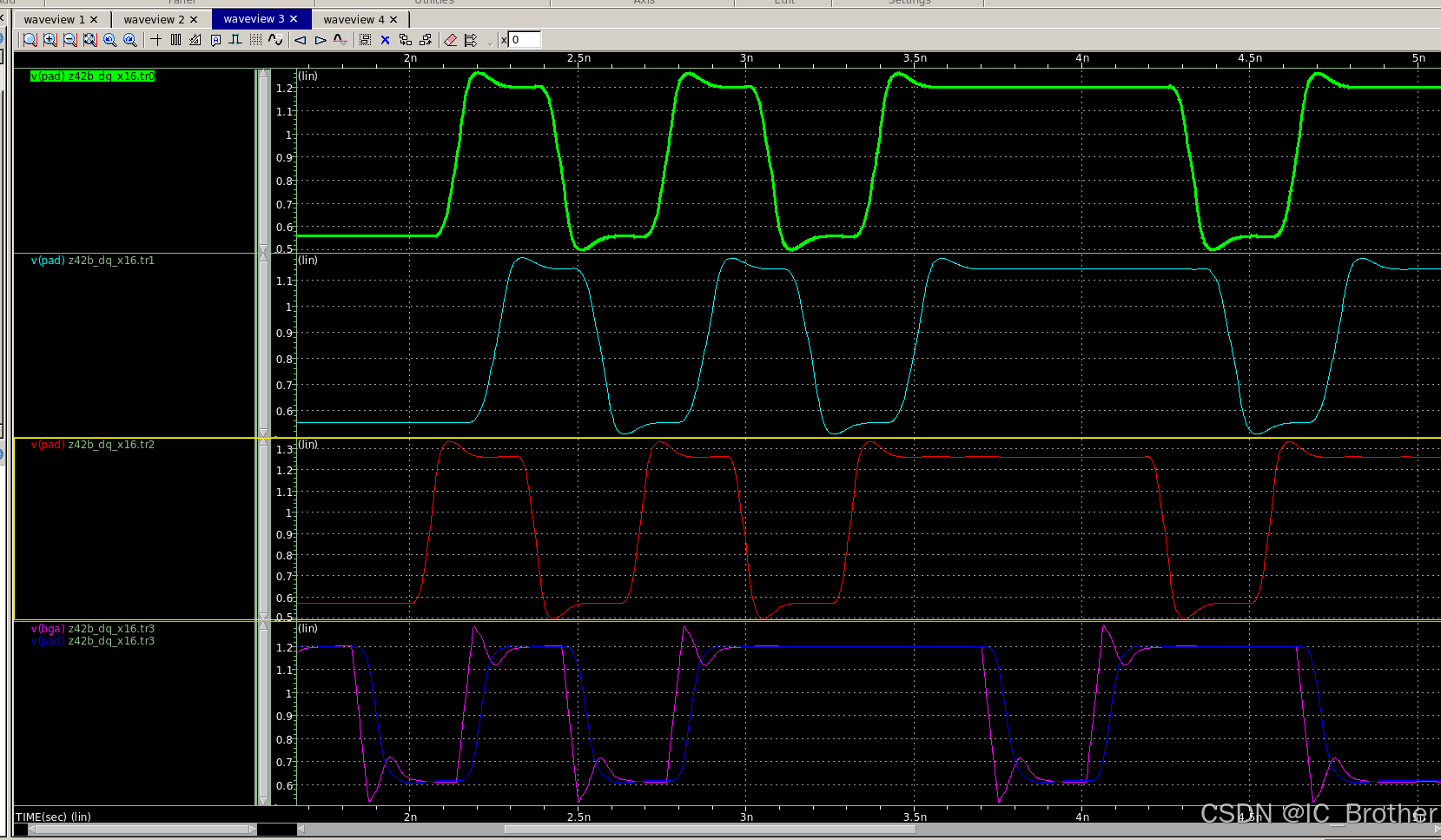

3)DDR4 IBIS model sim

input

dqs

dq

自动化脚本

1)Makefile脚本

all: run_vcs cleanTIME_SCALE = -timescale=1ps/1ps## -cm line+cond+tgl+fsm+branch+assertrun_vcs:vcs -f ddr4_tb.f \${TIME_SCALE} -sverilog -full64 -debug_access +all -ignore all -R -fsdb +define+FSDB -l rpt/ddr4_tb.log \-lca -kdb -ntb_opts \+npspecify \-reportstats -l rpt/ddr4_tb.rpt \-cm line+cond+fsm+branch+assertrun:vcs -f ddr4_tb.f \${TIME_SCALE} -sverilog -v2005 -full64 -ignore all -R -gui -l rpt/ddr4_tb.log \-reportstats -l rpt/ddr4_tb.rpt \run_verdi:verdi -ssf ddr4_tb.fsdb -f ddr4_tb.f -sv &cov:verdi -cov -covdir simv.vdb/ &clean:rm -rf csrc DVEfiles simv* *.vpd simv *.key novas* verdi* *.log vc_hdrs.h vdCovLog *.fsdb *.vector2)Python自动化脚本

通过python3获取pattern list,并行仿真后,收集仿真结果,部分示例如下。

pattern.list(部分)

依次为pattern name,DDR4 cfg,Speed

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_1250

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_1072

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_938

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_833

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_750

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_682

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_625

sim.log(部分)

Log Timestamp: 2024-10-07 21:51:59

Total Count: 588

Total Pass: 588

Total Fail: 0

=================================================================

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_1250 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_1072 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_938 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_833 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_750 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_682 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_625 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X8_TS_1250 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X8_TS_1072 : Pass

项目难度:⭐⭐⭐⭐⭐

项目推荐度:⭐⭐⭐⭐

项目推荐天数:28~35天

项目简介和资料

1)项目简介

本项目基于JEDEC JESD79-4 标准,完成了DDR4控制器接口的架构规划、RTL设计以及基础功能验证。整个项目分为两个主要部分:

1)基于Micron DDR4 仿真模型搭建基本DDR4协议初始化、Act、Write、Read等基础操作,帮助学习DDR4关键时序参数,快速了解DDR4 Spec,覆盖1600~3200Mbps、2 ~16G、X4/X8/X16全Spec应用场景。

2)使用System Verilog设计和测试DDR4控制器及高速接口。提供将命令、数据转换为DDR控制器和内存DDR4 DIMM使用的引脚信号电平,并在Testbench提供2Kb随机读写测试案例中用于验证DDR接口。

3)项目包含源文件、技术文档、Makefile脚本、Python脚本以及答疑,其中Python脚本支持一键搭建环境、VCS仿真、收集Report并汇总到日志文件。

4)项目还会额外提供丰富的DRAM基础资料,包含DDR4 Spec、DRAM电路设计教材、论文、专利等资料,对于有意向选择全定制存储的同学将会有一定帮助。

2)拓展资料

项目还额外提供DRAM设计相关资料,包含:

1)DRAM设计教材

2)DRAM设计论文及相关专利

3)16Gb DDR4 Hspice IBIS仿真模型及质量报告

软件环境要求

软件和EDA环境:

(1)操作系统:Centos

(2)EDA 软件:VCS-MX O-2018.09-1、Verdi_O-2018.09-SP2、HSPICE Version N-2017.12-SP2

(3)Python版本:Python 3.6.8

项目学习目的:

(1)熟练掌握复杂项目的工程管理;

(2)熟悉 Verilog HDL仿真以及Python自动化脚本工具;

(3)学习DRAM基本结构和基础原理;

(4)学习DDR4 Spec和基本时序参数;

(5)熟练掌握System Verilog语法和验证方法;

总结

整个项目涵盖了完整的DDR4控制器以及testbench设计,项目旨在设计和验证一个基于 SystemVerilog 的 DDR4 存储器模型和测试平台。项目核心包括:设计 DDR4 接口,构建模拟存储器的控制逻辑,创建测试平台(Testbench)进行功能、时序和性能验证。通过使用状态机来模拟命令和数据传输,利用 VIP 模块生成各种操作并进行协议检查,确保模型符合 DDR4 标准。在验证过程中,涵盖了读写操作、时序约束、性能测试等,确保最终验证环境全面、可靠。相对先前列出的开源和初级项目来说,整体难度偏高,适合缺少验证及高速接口相关项目经验的求职者。

特地注明:整个项目耗费较长的周期和个人精力,项目收费并且保证独一无二(性价比肯定是重要因素,毕竟都有过学生时代)。感兴趣的同学可以通过私信联系,我始终相信好的知识和项目肯定是收费的,网上也有很多类似的课程和项目,但大多数没有从完整的项目需求出发,代码和工程重复率高,不少同学往往是花了很多钱,却没有学到真正的东西。