目录

一、背景

二、Max/Min_delay约束

2.1 约束设置参数

2.2 约束说明

三、场景说明

3.1 路径分段

3.1.1 无效的约束对象

3.1.2 设计代码

3.2 有效的约束对象

3.3 datapath only

3.3.1 工程设计

3.3.2 datapath only报告

3.4 clock group约束优先级

3.4.1 MAX/MIN约束对象正确

3.4.2 MAX/MIN约束对象非时序起点/终点

一、背景

正常情况下FPGA设计中,内部路径通常需要时钟周期约束(create_clock)和时钟组约束(set_clock_groups),但对于一些特殊场景则需要时序例外约束,set_max_dealy和set_max_delay就是四大时序例外约束中的两个。

二、Max/Min_delay约束

在设计中,有时需要限定路径的最大时延和最小时延,如没有特定时钟关系的异步信号,但需要限制最大时延和最小时延,也可以对端口到端口(中间无寄存器)的路径设置最大时延和最小时延,设置最大时延和最小时延会影响路径的setup和hold时序分析,它会覆盖默认的时序约束。

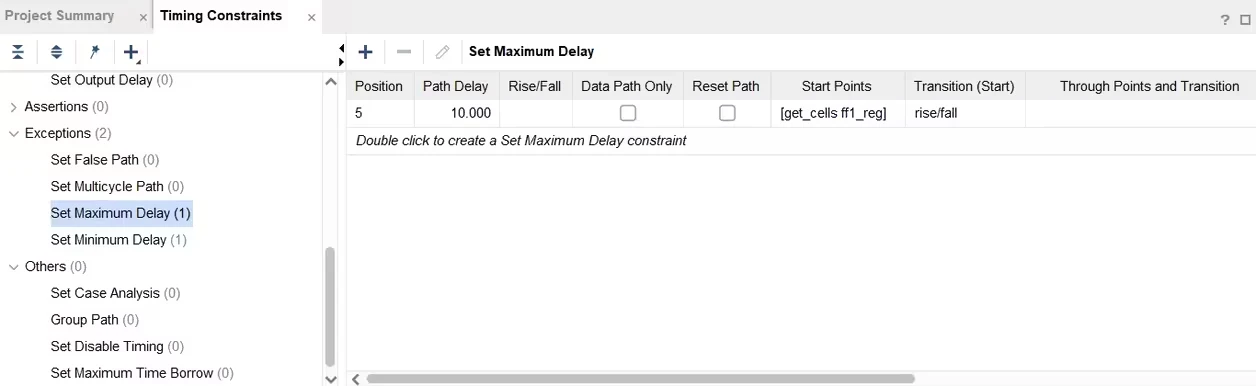

设置路径最大时延和最小时延的命令为set_max_delay,set_min_delay,可在Timing Constraints窗口进入Exceptions中,选择Set Maximum Delay或Set Minimum Delay,即为选择最大时延或最小时延。

2.1 约束设置参数

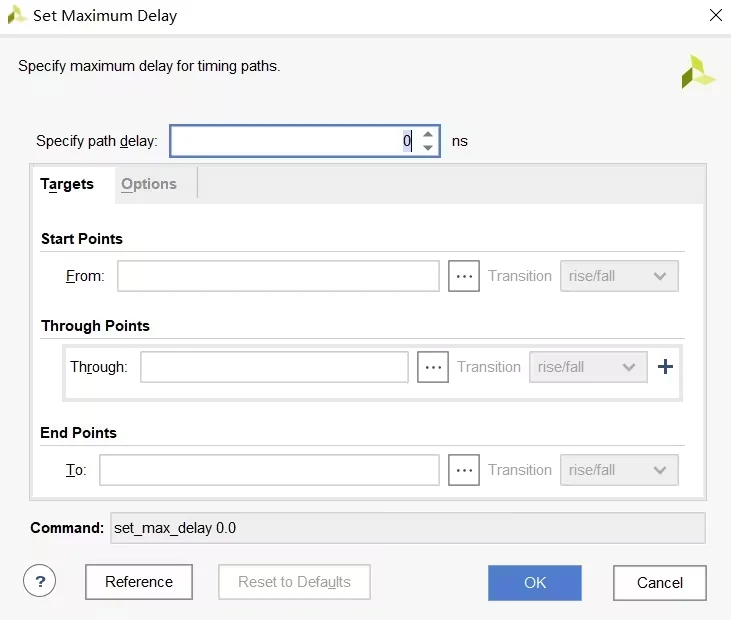

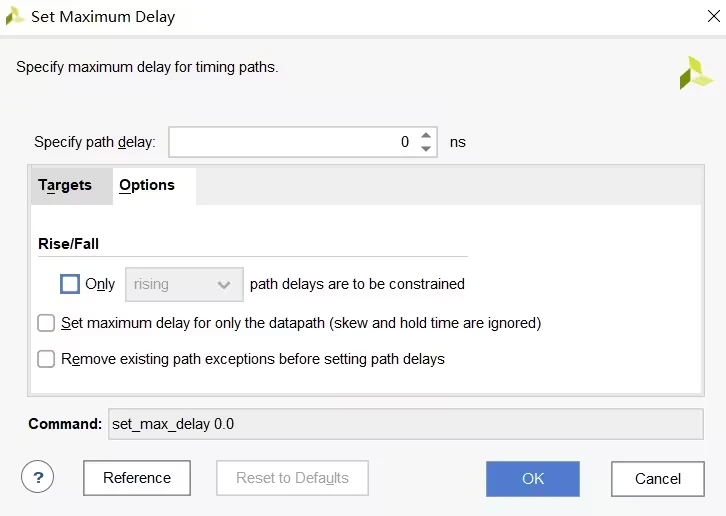

以设置最大时延为例,双击Set Maximum Delay进入设置窗口

Targets设置

Specify path delay:设置路径最大时延值,可为正整数或负整数

From:设置路径的起点,对象可以是Clocks,Cells,Cell pins,I/O ports

Through:设置路径的中间经过点,对象可以是Net,Cells,Cell pins

To:设置路径的终点,对象可以是Clocks,Cells,Cell pins,I/O ports

Options设置

Rise/Fall:勾选后可设置最大时延只对上升沿触发或下降沿触发的路径有效,未勾选时不区分边沿触发。

Set Maximum delay for only the datapath:勾选后设置的时延约束只对数据路径有效,时钟偏斜和hold检查会被忽略,即等效于该路径也设置了set_false_path -hold约束,此时如果约束中设置了set_min_delay约束也不会生效。并且该设置不能用于set_min_delay约束中。

Remove existing path exceptions before setting path delays:勾选后,如果设置的约束路径上有其他时例外约束(如false_path,multicycle约束,最大最小时延约束都将被移除)

2.2 约束说明

set_max_delay/set_min_delay应用场景之一是用于约束输入端口和输出端口间的纯组合逻辑路径。

set_max_delay另一个常用的场景是没有时钟关系的异步信号,但需要设置最大时延。两个异步时钟路径可以使用set_clock_group或set_false_path,从而不会进行时序分析。当异步时钟间的设计合理,如FIFO中的两级同步寄存器,要放宽约束,保证两个时钟间的路径延时符合实际情况,就需要使用set_max_delay。

在多比特跨时钟域(CDC)场景中,比特之间的偏斜必须在一定要求时间内,虽然偏斜可以通过set_bus_skew来约束,但必须确保两个时钟域间的时延不能太大。此时可以通过约束set_max_delay -datapath_only代替set_false_path/set_clock_groups。

如果对于两个时钟域间的部分路径或全部路径的最大时延必须明确时,就必须使用set_max_delay -datapath_only约束。这种场景下,set_clock_groups不能用来定义两个时钟作为异步时钟,因为从约束的优先级角度看它将取代set_max_delay。其他跨时钟域路径就必须联合约束set_false_path或set_max_delay约束。

三、场景说明

3.1 路径分段

不同于约束文件XDC中的其他约束,在设置最大时延和最小时延中,参数-from和-to选项为设置约束的起点和终点,在设置时,有些起点和终点对于约束来说是无效的。当设置了一个无效的起点时,为了让节点成为一个有效的起点,时序分析工具会阻止时序路径通过该节点。

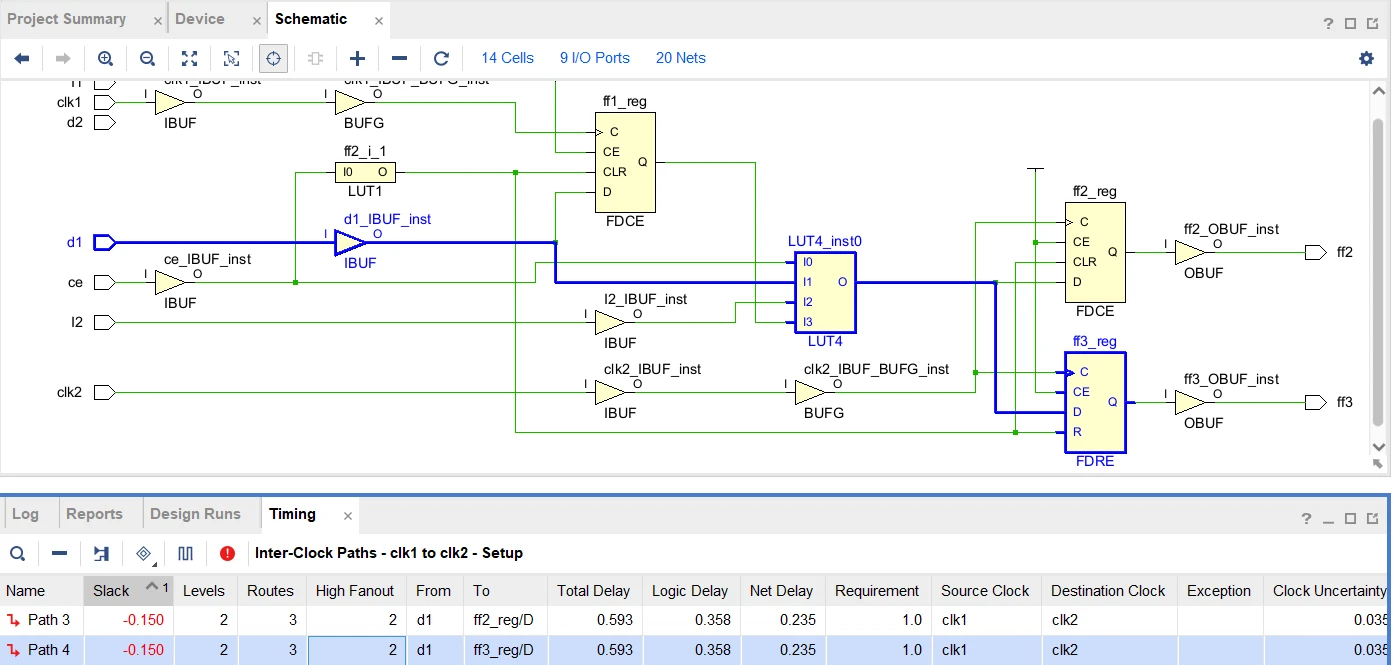

以schematic如下图的路径为例,d1存在到ff2_reg和ff3_reg的时序路径

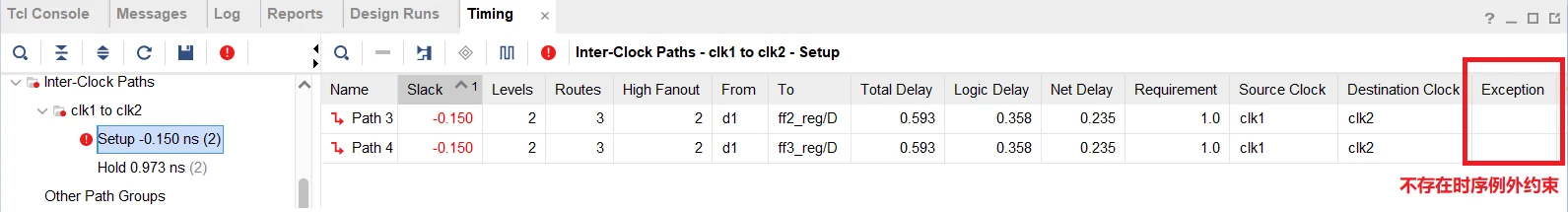

未设置max/min delay约束时,存在d1到ff2_reg/D和ff3_reg/D的时序路径

添加d1到ff2_reg/D的max delay约束,约束的from和to为有效的时序起点和终点

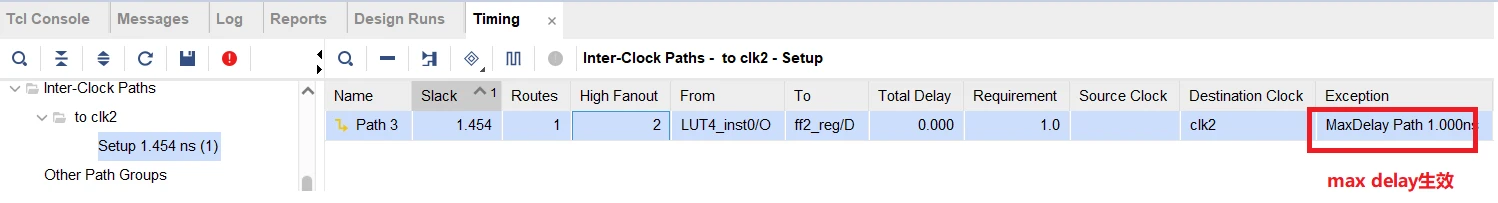

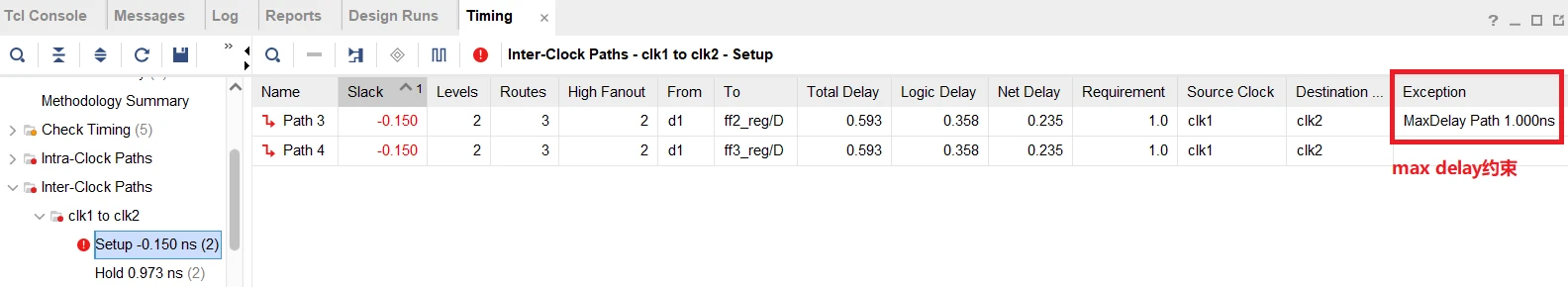

set_max_delay -from [get_ports d1] -to [get_pins ff2_reg/D] 1.0时序报告如下,d1到ff2_reg/D和ff3_reg/D的路径依旧有效

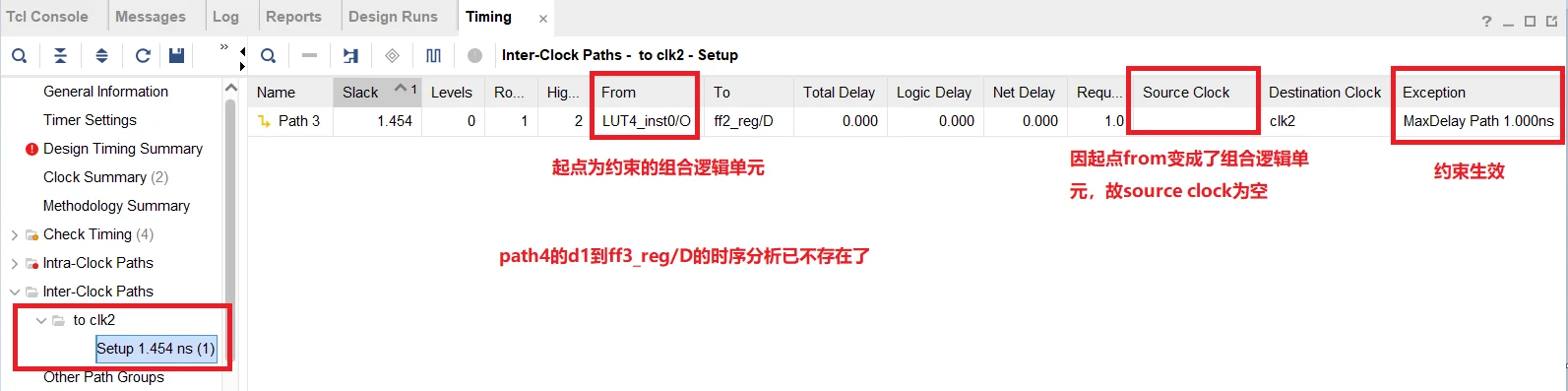

3.1.1 无效的约束对象

如果约束中的对象非时序路径的起点或终点,则会将该对象强制设置为时序路径的起点或终点,但可能引入路径分段从而导致其他时序路径断开。如约束的起点为组合逻辑单元

set_max_delay -from [get_pins LUT4_inst0/O] -to [get_pins ff2_reg/D] 1.0时序报告如下,因为将LUT4_inst0/O强制设为起点,导致其他经过该单元的路径将会断开,因此不存在d1到ff3_reg/D的时序路径,同时也不存在对应的hold路径

3.1.2 设计代码

module MAX_MIN(d1,d2,clk1,clk2,ce,I1,I2,ff2,ff3);

input d1,d2,clk1,clk2,ce,I1,I2;

output ff2,ff3;

reg ff1,ff2,ff3;

wire comb,comb1,comb2;

always@(posedge clk1,negedge ce)

beginif(!ce)beginff1<=0;endelse beginff1<=d1;end

end

//assign comb=ff1&d2;LUT4 #(.INIT(16'h0101) // Specify LUT Contents) LUT4_inst0 (.O(comb1), // LUT general output.I0(ce), // LUT input.I1(d1), // LUT input.I2(I2), // LUT input.I3(ff1) // LUT input);always@(posedge clk2,negedge ce)

beginif(!ce)ff2<=0;else beginff2<=comb1;end

endLUT4 #(.INIT(16'h0111) // Specify LUT Contents) LUT4_inst (.O(comb2), // LUT general output.I0(ce), // LUT input.I1(I1), // LUT input.I2(I2), // LUT input.I3(comb) // LUT input);always@(posedge clk2)

beginif(!ce)ff3<=0;else beginff3<=comb1;end

end

endmodule

3.2 有效的约束对象

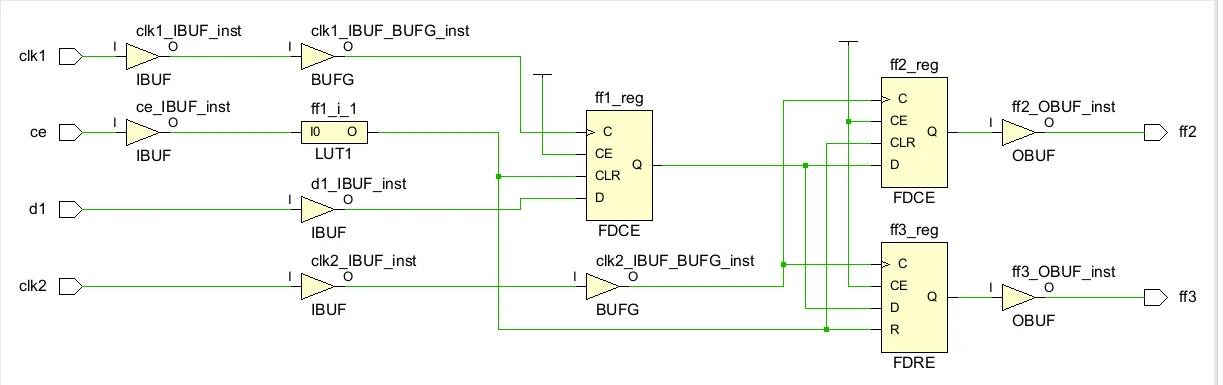

工程设计如下

module MAX_MIN(d1,clk1,clk2,ce,ff2,ff3);

input d1,clk1,clk2,ce;

output ff2,ff3;

reg ff1,ff2,ff3;

always@(posedge clk1,negedge ce)

beginif(!ce)beginff1<=0;endelse beginff1<=d1;end

endalways@(posedge clk2,negedge ce)

beginif(!ce)ff2<=0;else beginff2<=ff1;end

endalways@(posedge clk2)

beginif(!ce)ff3<=0;else beginff3<=ff1;end

end

endmoduleschematic图如下,设计简单,即ff1_reg到ff2_reg和ff3_reg的两条路径

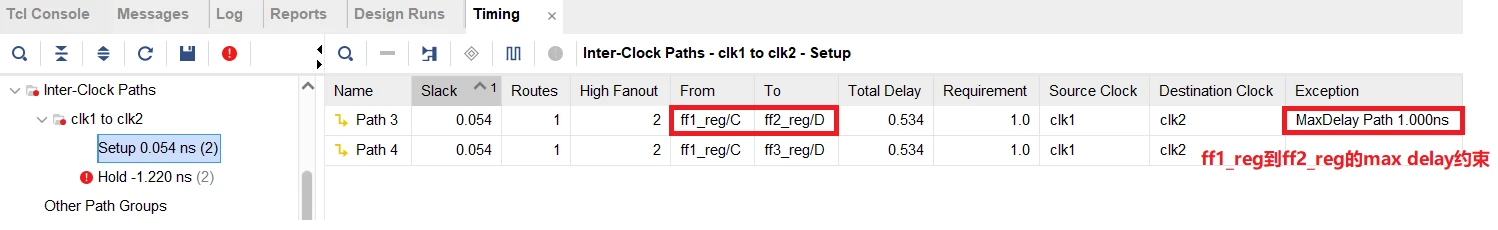

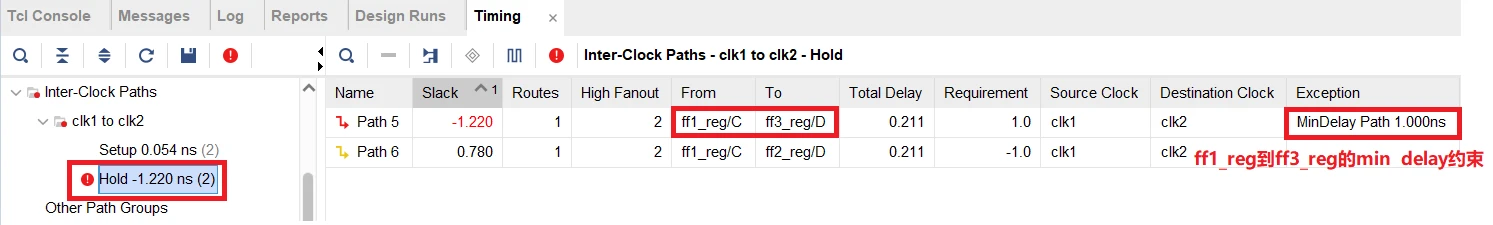

对ff1_reg到ff2_reg和ff3_reg分别设置max delay和min delay约束

create_clock -period 10.000 -name clk1 -waveform {1.000 6.000} [get_ports clk1]

create_clock -period 8.000 -name clk2 -waveform {0.000 4.000} [get_ports clk2]

set_max_delay -from [get_pins ff1_reg/C] -to [get_pins ff2_reg/D] 1.0

set_min_delay -from [get_pins ff1_reg/C] -to [get_pins ff3_reg/D] 1.0max delay生效于setup分析中,min delay生效于hold分析中

3.3 datapath only

datapath only表示分析时序slack时只考虑数据路径上的时延,不分析source clock和destination clock的时钟延时

3.3.1 工程设计

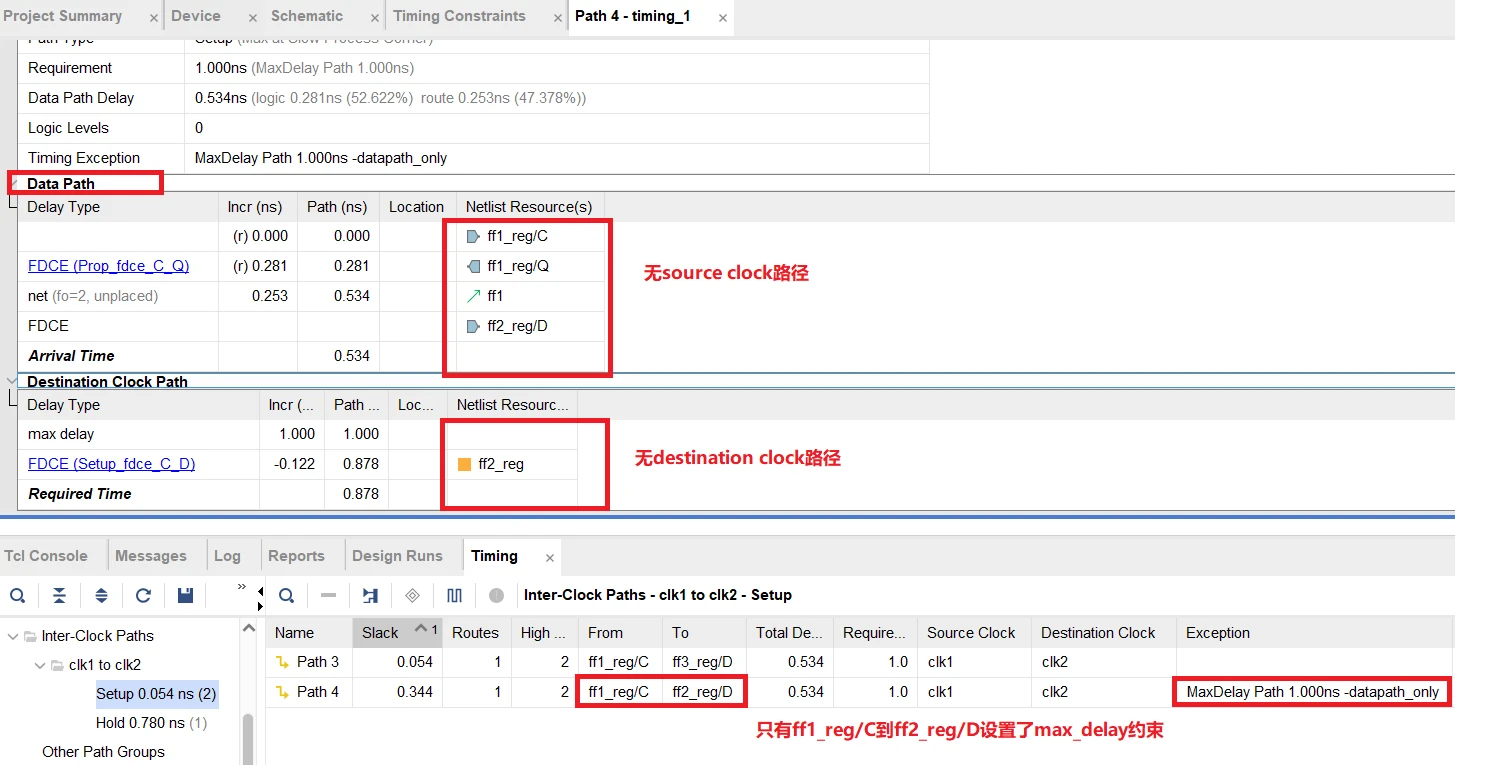

工程设计同上述有效约束对象章节的代码一致,对ff1_reg/C到ff2_reg/D的路径设置set_max_delay datapath_only约束

create_clock -period 10.000 -name clk1 -waveform {1.000 6.000} [get_ports clk1]

create_clock -period 8.000 -name clk2 -waveform {0.000 4.000} [get_ports clk2]

set_max_delay -datapath_only -from [get_pins ff1_reg/C] -to [get_pins ff2_reg/D] 1.03.3.2 datapath only报告

在path report中,因ff1_reg/C到ff2_reg/D设置了max delay,所以没有source clock和destination clock路径

查看hold中时序结果,只有ff1_reg/c到ff3_reg/D的路径,符合预期

3.4 clock group约束优先级

3.4.1 MAX/MIN约束对象正确

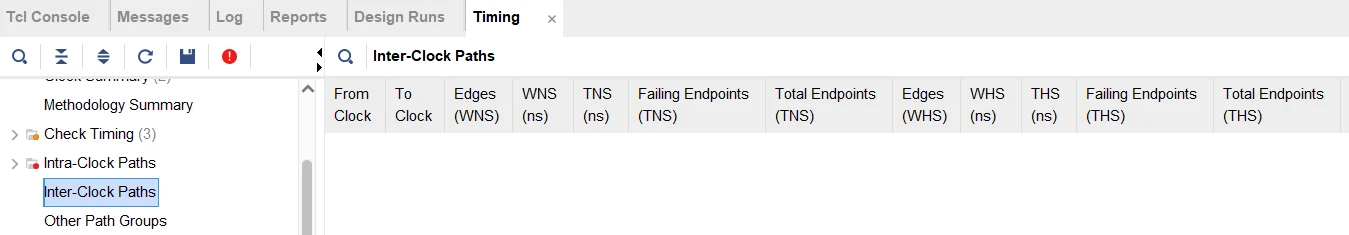

在set_max_delay/set_min_delay的from/to为有效的时序路径起点和终点时,对路径设置set_clock_group约束,此时set_clock_group优先级更高。

依旧采用3.2小节的设计,约束如下,clk1和clk2通过set_clock_group设置为异步时钟,max delay约束对象为时序起点的ff1_reg/C

create_clock -period 10.000 -name clk1 -waveform {1.000 6.000} [get_ports clk1]

create_clock -period 8.000 -name clk2 -waveform {0.000 4.000} [get_ports clk2]

set_max_delay -from [get_pins ff1_reg/C] 1.0

set_min_delay -from [get_pins ff1_reg/C] 0.5

set_clock_groups -name clk_group -asynchronous -group [get_clocks clk1] -group [get_clocks clk2]时序报告inter clock paths中已不存在clk1到clk2的时序路径,即set_clock_groups的优先级更高,已将set_max_delay/set_min_delay覆盖

3.4.2 MAX/MIN约束对象非时序起点/终点

在set_max_delay/set_min_delay的from/to为有效的时序路径起点和终点时,对路径设置set_clock_group约束,此时set_max_delay/set_min_delay优先级更高。

采用3.1小节的设计,约束如下,clk1和clk2设置为异步时钟,max delay约束对象为非时序起点的LUT4_inst0/O

create_clock -period 10.000 -name clk1 -waveform {1.000 6.000} [get_ports clk1]

create_clock -period 8.000 -name clk2 -waveform {0.000 4.000} [get_ports clk2]

set_input_delay -clock [get_clocks clk1] 1.000 [get_ports {d1 d2}]

set_max_delay -from [get_pins LUT4_inst0/O] -to [get_pins ff2_reg/D] 1.0

set_clock_groups -name clk_group -asynchronous -group [get_clocks clk1] -group [get_clocks clk2]此时报告中依旧存在max delay的路径