FMC+ AD 子卡 12bit 2 通道 5.2GS/s 或单通道 10.4GS/s,是一款高分辨率、高采样率 ADC FMC+ 子板。它提 供 2 路 12 位 5.2GS/s 或 1 路 10.4GS/s 的 A/D 通 道 , 全功率模拟 -3dB 输入带宽可达 8GHz。本产品是基于 TI 公司ADC12DJ5200 模数转换芯片而设计。板卡支持触发输出/ 输入; 外触发 / 同步选择和内部参考、外部参考和载板参考三种时钟方式,可通过 3 个载板控制的 IO 信号实现时钟源选择。 板卡的电气与机械设计依据 FMC+ 标准 (ANSI/VITA 57.4),通过一个 HSPC 高速连接器连接至 FPGA 载板。前面板 I/O 装配 5 个 SSMC 同轴连接器。板卡设计了风冷和导冷版本,可适应于多种 FPGA 载板,如 Xilinx 和 Altera 等支持 FMC+ 的通用载板,以进行高性能的算法计 算。

主要指标

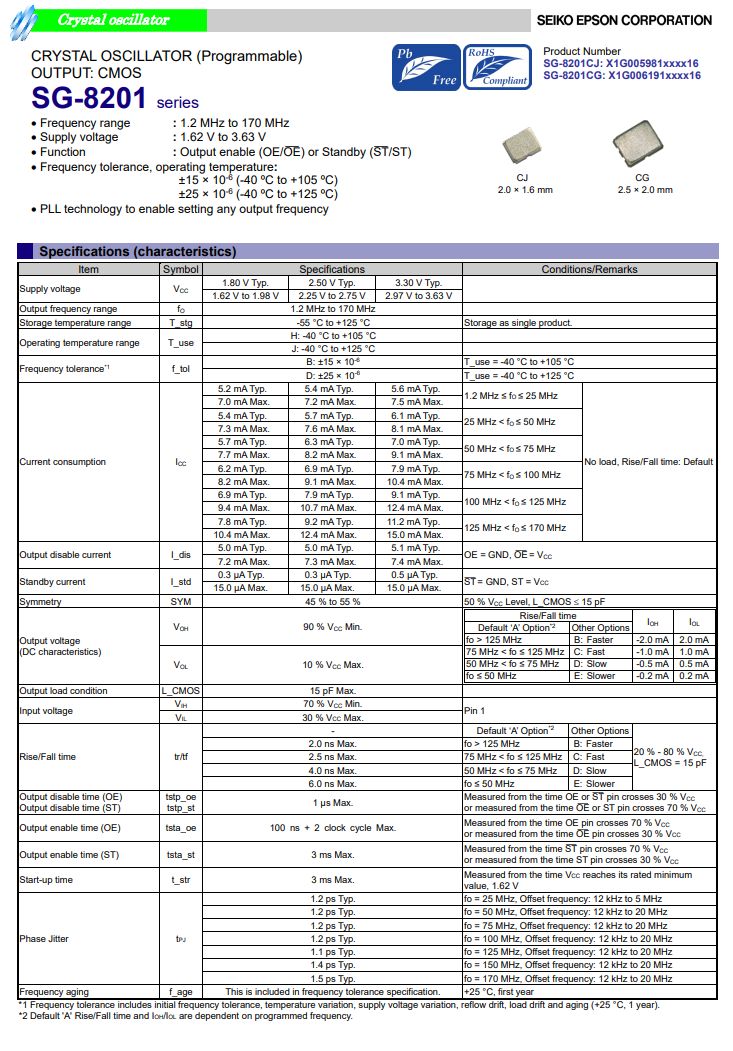

- 模拟输入带宽(-3 dB):8GHz

- 全量程输入电压:480mVpp ~ 1040mVpp(缺省值 0.8Vpp)

- FCLK =5120Mhz,AIN = –1 dBFS,双通道模式(JMODE3), VFS = 0.8 Vpp

FIN = 347MHz/2397MHz/5997MHz/7997MHz

— SNR:55.1/54.1/50.4/48.6 (dBFS)

— SINAD:54.4/53.4/48.6/46.2 (dBFS)

— SFDR:68/67/55/53 (dBFS)

— ENOB:8.7/8.6/7.8/7.4 (bits)

- FCLK =5120Mhz,AIN = –1 dBFS,单通道模式(JMODE1), VFS = 0.8 Vpp

FIN = 347MHz/2397MHz/5997MHz/7997MHz

— SNR:55.1/54.1/50.5/48.6 (dBFS)

— SINAD:53.9/51.7/47.6/45.0 (dBFS)

— SFDR:68/60/55/52 (dBFS)

— ENOB:8.7/8.3/7.6/7.2 (bits)

特性:

- 5 个 SSMC 的连接器,其中 2 个分别为模拟信号输入 1 (AD0)和模拟信号输入 2 (AD1);一个为外部参考时钟输入通道(RCK);一个为触发输入 / 输出通道 (TRG);一个为触发 / 同步输入通道 (SYN)。

- 采样频率:12bit,2 通道 5.2GS/s 或 1 通道 10.4GS/s。

- 带宽:全功率模拟带宽(-3 dB)8GHz。

- 适应范围:完全符合 Vita57.4 规范,包括结构件,子卡尺寸, 面板连接器,正反面器件的限高等,大大提供了子卡的通用性和适配性。

- 多种散热方式:风冷或导冷。

- AC 耦合输入。

- 时钟选择灵活:内参考时钟、外参考时钟、载板参考时钟选择可由载板控制。

- HSPC 高速连接器。

- 工作温度:商业级 0℃~ +55℃ ,工业级 -20℃~ +65℃。

其他支持

- 提供 Verilog bit 文件

- JESD204B Core,可包括 BSP