本例程使用ZC706加ADRV9009修改HDL项目,在vivaod中使用ila实时抓取两路接收波形。

将网盘链接中的BOO.BIN文件复制到SD卡中,插入开发板,并将开发板的启动模式设置为SD卡启动。插入电源,JTAG和串口。

在NO-OS的ADRV9009的项目中,默认接收的频率为2G,所以需要使用信号发生器产生一个稍微大于2G的信号。本实验使用信号发生器产生一个2.004G的信号,使用射频转接头将同一个信号源链接到两个ADRV9009的接收端。

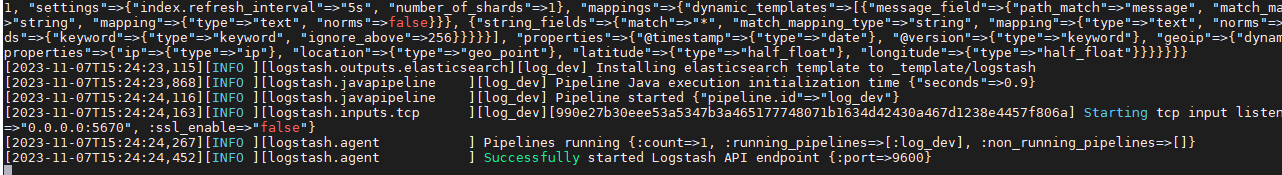

开启电源,串口输出内容如下所示:

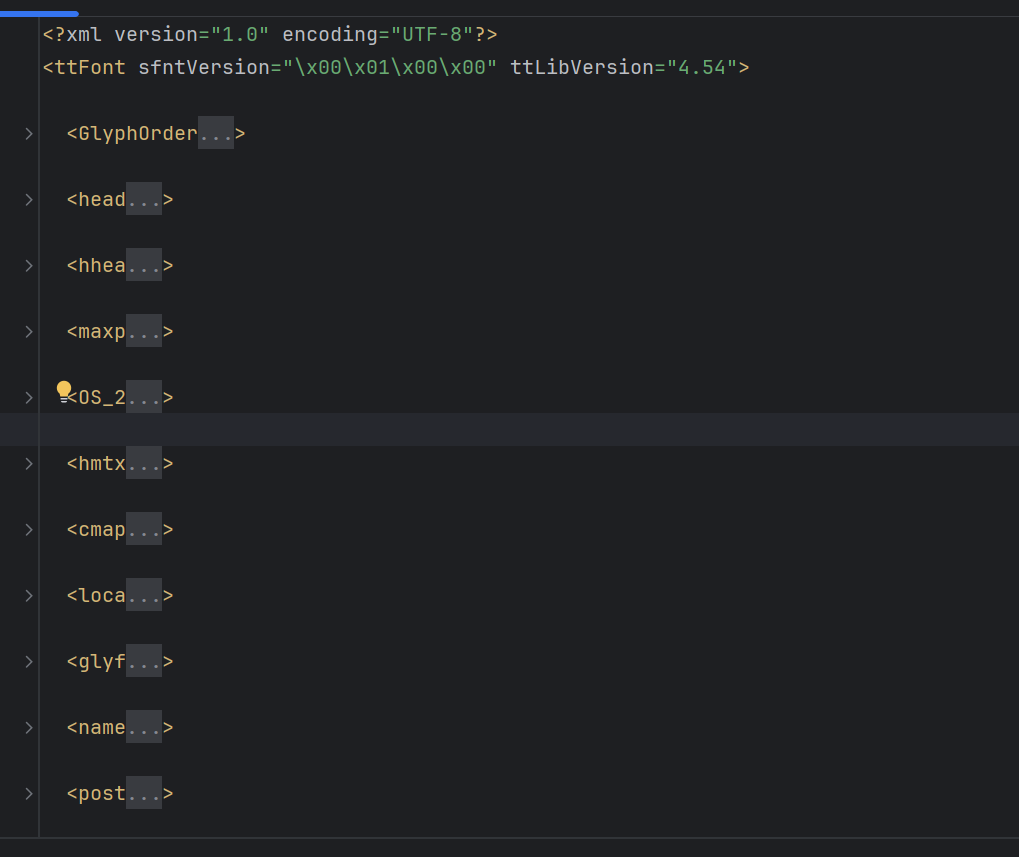

打开vivado—>open Hardware Manager

识别出硬件设备

添加ltx文件,同在网盘链接中

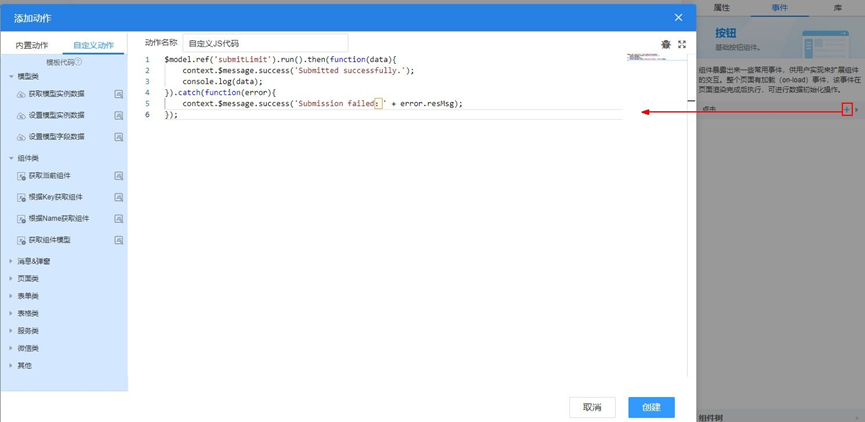

设置信号显示模式为有符号的十进制。

显示模式设置为Analog

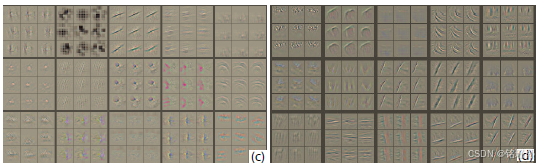

点击抓取,波形如下所示,可以看到有四路波形,上面两路是一组(一路实部一路虚部),下面两路是一组。若只连一个接收通道那就只有一组波形,可以拔下来插到另一个通道上在进行抓取。若出现波形很低的情况,可以把信号发生器关闭,板子重新上电,抓取一次杂波后在打开信号发生器。