SRIO IP调试问题记录(ready信号不拉高情况)

问题:调试过程中遇到有时写入数据后数据不发送,并且ready信号在写入一定数据后一直拉低的情况(偶发,不是每次必然出现)。buf空间设置为16时,写入15包数据,写完第16包包头后,ready信号一直为低;buf空间设置为32时,写入31包数据,写完第32包包头后,ready信号一直为低。

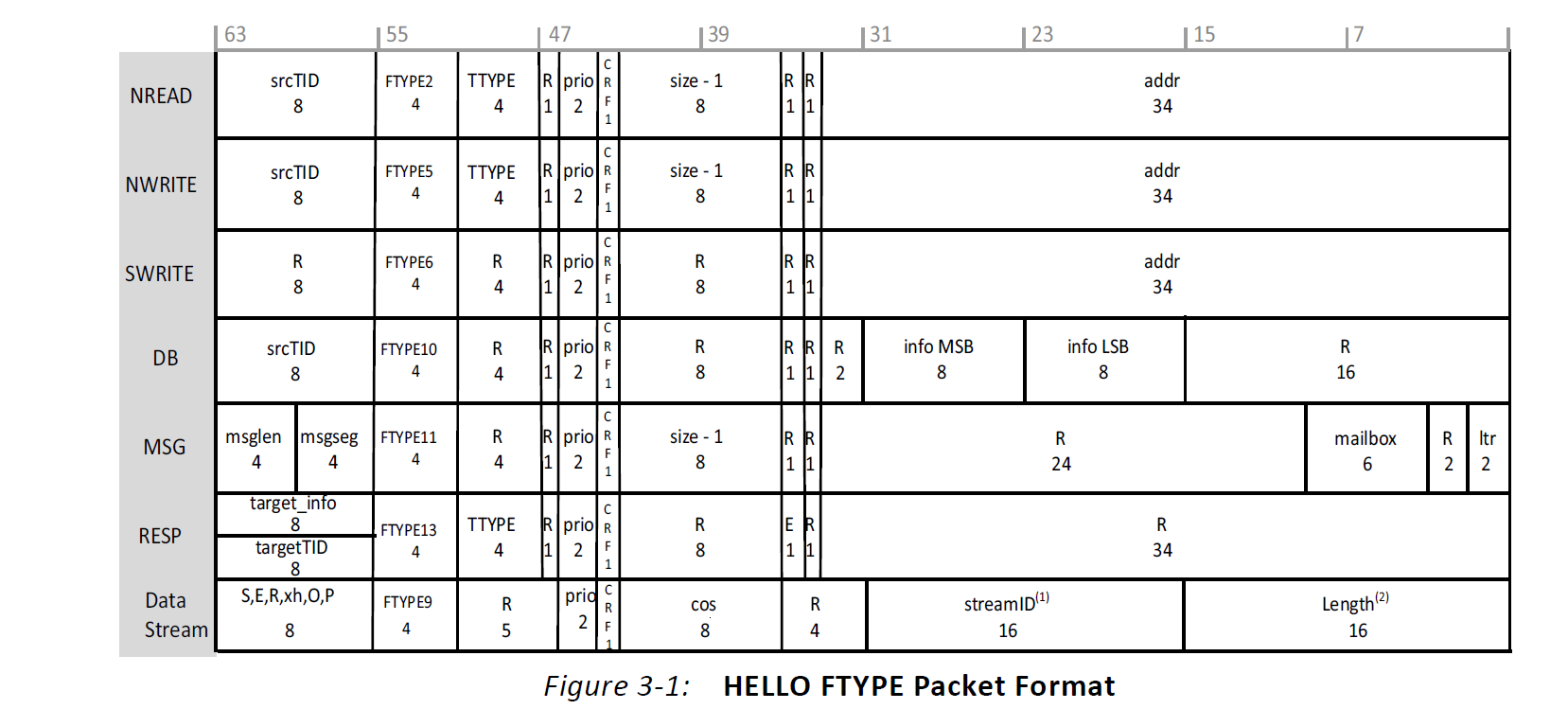

原因:写入AXI总线的数据包格式不正确,需要核对数据包头是否满足SRIO包头格式。数据包格式不正确时数据会一直存在buf中,直到buf空间写满,buf空间写满后ready信号一直为低电平。该问题不是每次必然出现的原因为写如SRIO包头处时序不稳定,有时能正确写入包格式,有时不能正确写入包格式,所以才偶发出现故障。各消息类型包头如下:

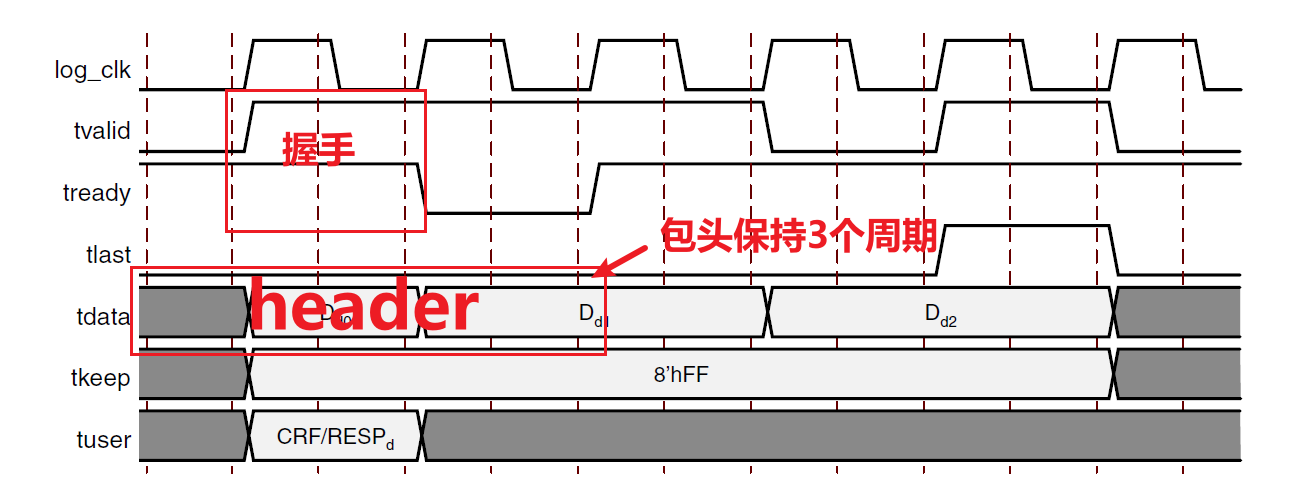

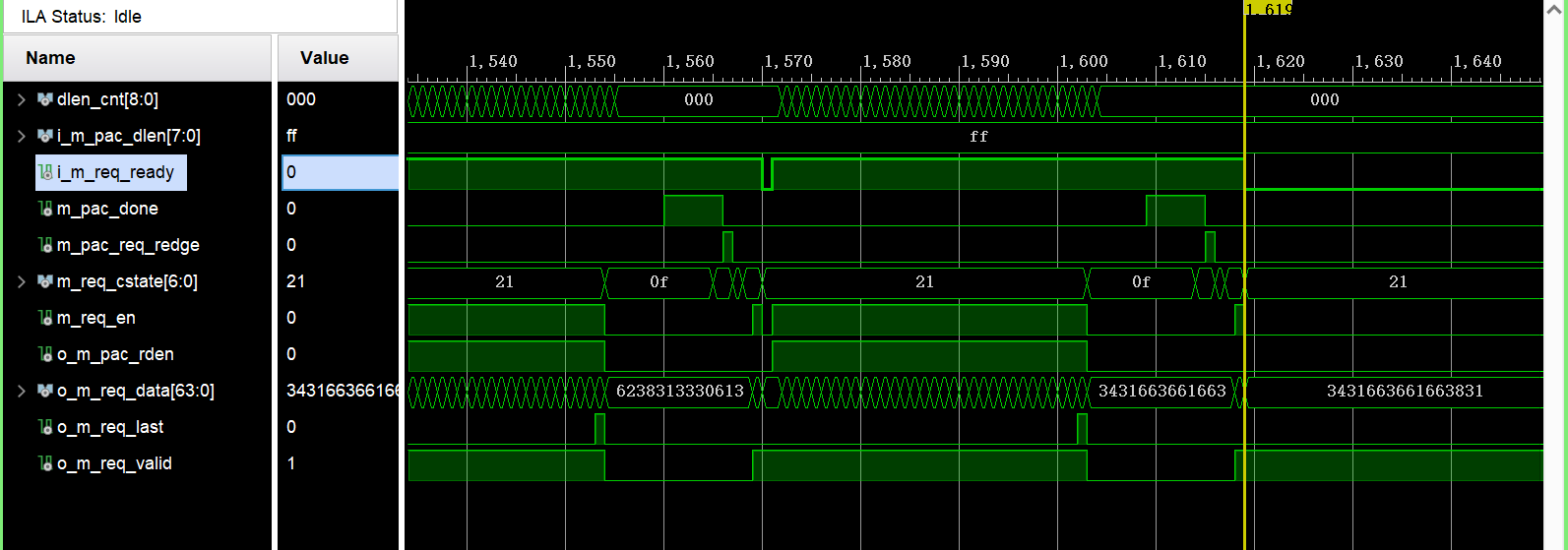

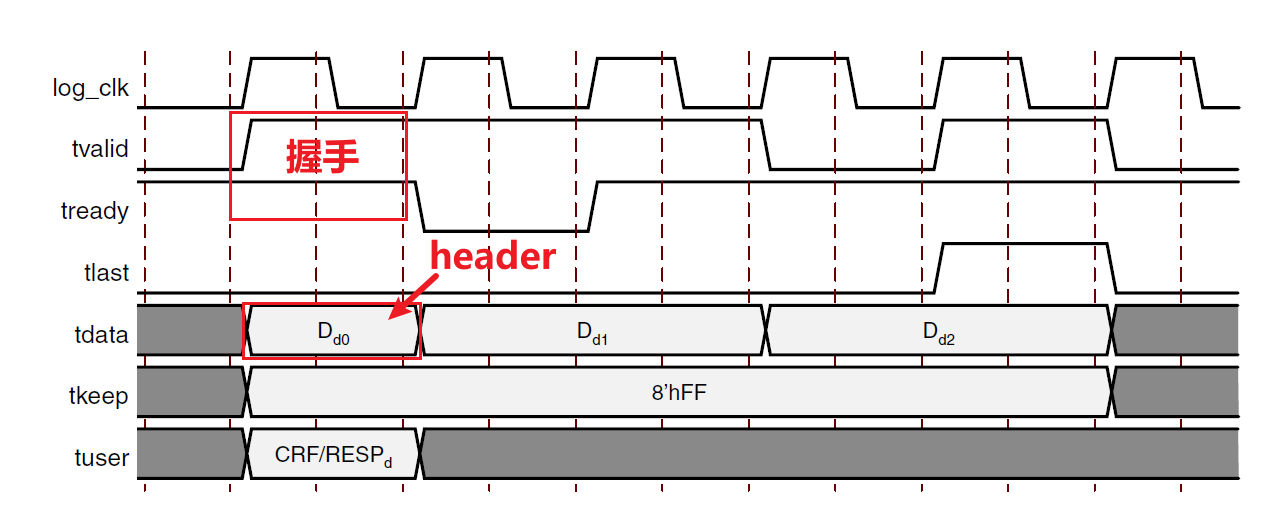

解决方法:使用ILA抓取波形发现,包头数据只保持了一个时钟周期,该工程占用FPGA资源较多,代码量较大,可能导致布局布线后时序不稳定。解决方法为在ready和vaild信号握手前将包头数据提前放到数据总线data上,握手以后也可以再维持一个周期的包头数据,然后再进行数据传输。包头数据在data上维持3个周期,ready和vaild信号在第二个周期进行握手,这样包头信号就不会出现时序不稳定情况。

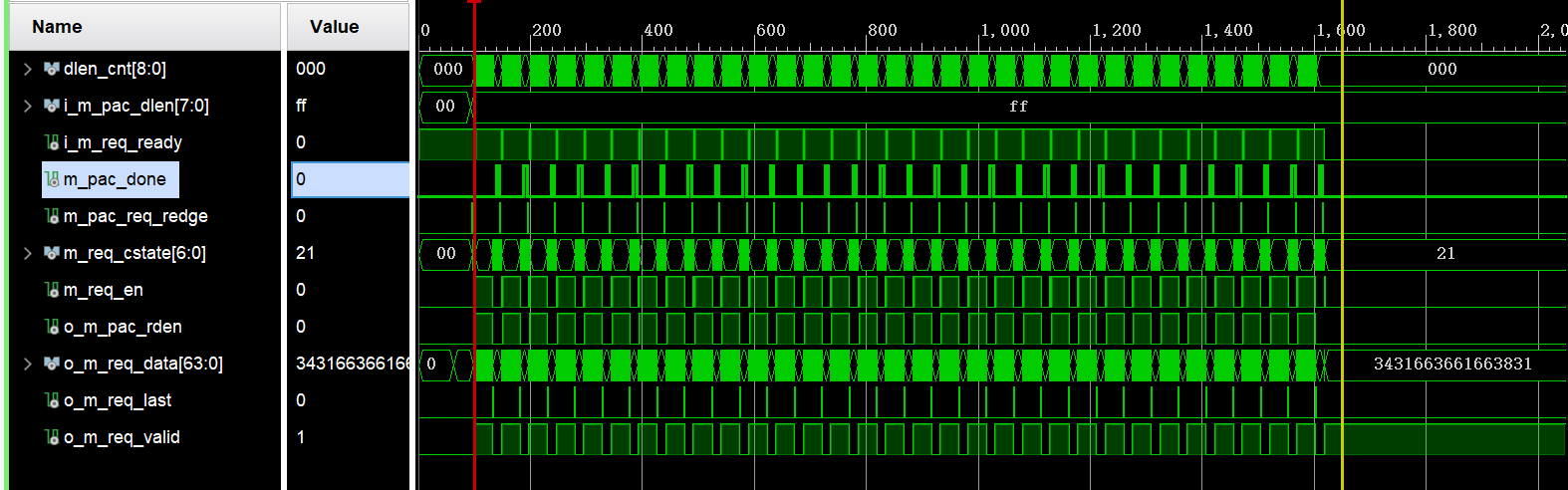

改之前,在数据发送模块抓出的波形和手册时序一致:

改之后: