名称:BPSK调制verilog

软件:Quartus

语言:Verilog

要求:

一、设计说明

BPSK调制广泛应用于卫星通信、移动通信等领域。本题目要求设计一个基于直接数字频率合成技术的BPSK调制器,实现对输入周期数字比特流的BPSK调制。

二、设计要求

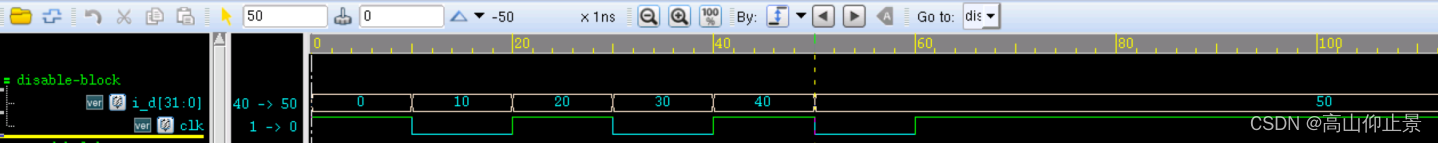

1. 输入数字比特流波形和输出BPSK调制波形必须能够通过示波器或在ModelSim中观测到。

2. 调制器输入数字比特流的速率不低于10kbps。

3. 使用ALTERA公司的FPGA器件进行开发。

4. 可根据情况增加其他功能。

代码下载:BPSK调制verilog_Verilog/VHDL资源下载

代码网:hdlcode.com

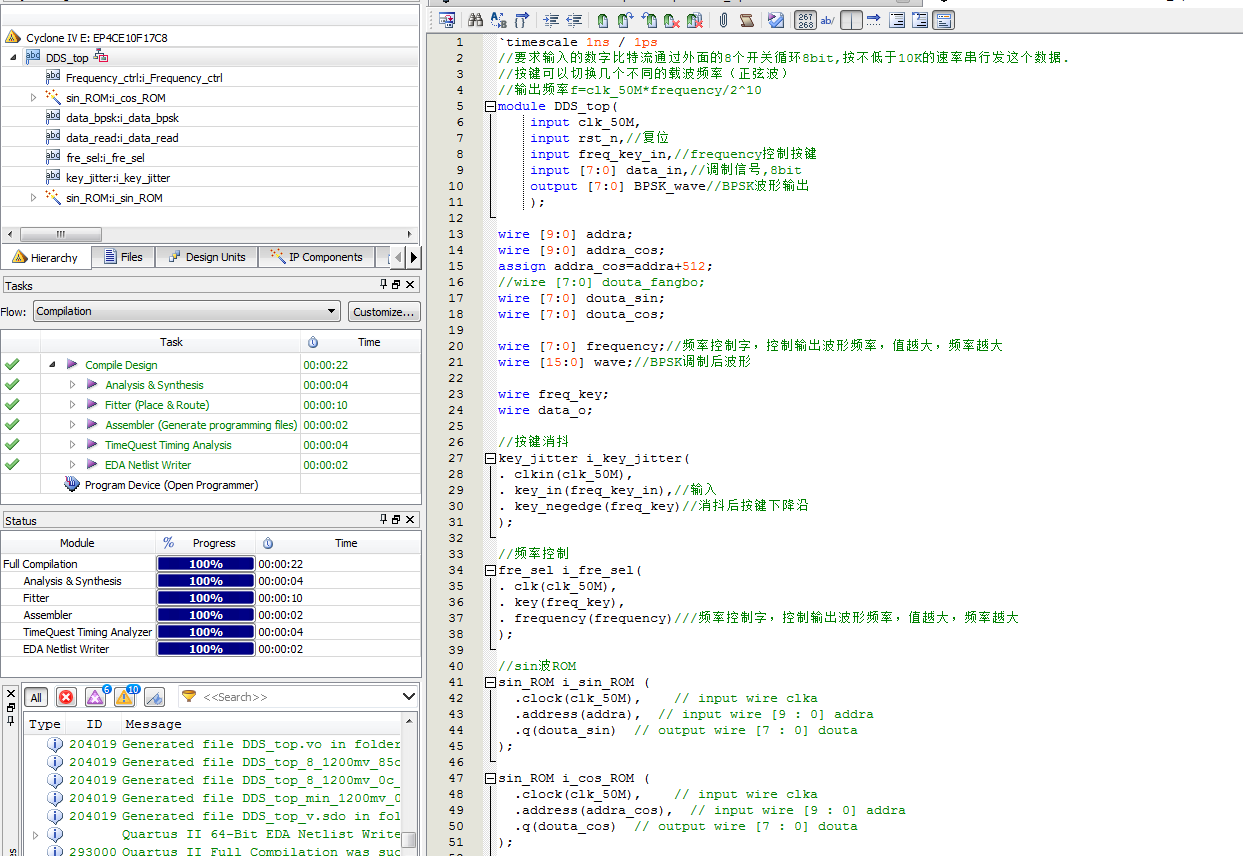

部分代码展示

`timescale 1ns / 1ps //要求输入的数字比特流通过外面的8个开关循环8bit,按不低于10K的速率串行发这个数据. //按键可以切换几个不同的载波频率(正弦波) //输出频率f=clk_50M*frequency/2^10 module DDS_top(input clk_50M,input rst_n,//复位input freq_key_in,//frequency控制按键input [7:0] data_in,//调制信号,8bitoutput [7:0] BPSK_wave//BPSK波形输出); wire [9:0] addra; wire [9:0] addra_cos; assign addra_cos=addra+512; //wire [7:0] douta_fangbo; wire [7:0] douta_sin; wire [7:0] douta_cos; wire [7:0] frequency;//频率控制字,控制输出波形频率,值越大,频率越大 wire [15:0] wave;//BPSK调制后波形 wire freq_key; wire data_o; //按键消抖 key_jitter i_key_jitter( . clkin(clk_50M), . key_in(freq_key_in),//输入 . key_negedge(freq_key)//消抖后按键下降沿 ); //频率控制 fre_sel i_fre_sel( . clk(clk_50M), . key(freq_key), . frequency(frequency)///频率控制字,控制输出波形频率,值越大,频率越大 ); //sin波ROM sin_ROM i_sin_ROM (.clock(clk_50M), // input wire clka.address(addra), // input wire [9 : 0] addra.q(douta_sin) // output wire [7 : 0] douta ); sin_ROM i_cos_ROM (.clock(clk_50M), // input wire clka.address(addra_cos), // input wire [9 : 0] addra.q(douta_cos) // output wire [7 : 0] douta ); //频率累加器 Frequency_ctrl i_Frequency_ctrl( . clk_50M(clk_50M), . rst_n(rst_n & freq_key_in), . frequency(frequency),//频率控制字 . addra(addra)//输出地址);//调试信号输出 //输入的数字比特流通过外面的8个开关循环8bit,按不低于10K的速率串行发这个数据. data_read i_data_read( . clk_50M(clk_50M), . rst_n(rst_n & freq_key_in),//复位 . data_in(data_in),//调制信号,8bit . data_o(data_o)//串行输出信号 ); //调制模块 data_bpsk i_data_bpsk( . clk_50M(clk_50M), . rst_n(rst_n & freq_key_in),//复位 . data_o(data_o),//调制信号 . douta_sin(douta_sin),//sin . douta_cos(douta_cos),//cos . BPSK_wave(BPSK_wave)//BPSK波形输出 );

设计文档(文档点击可下载):

本要求设计一个基于直接数字频率合成技术的BPSK调制器的FPGA IP核,实现对输入周期数字比特流的BPSK调制,其中调制器输入数字比特流的速率不低于10kbps。

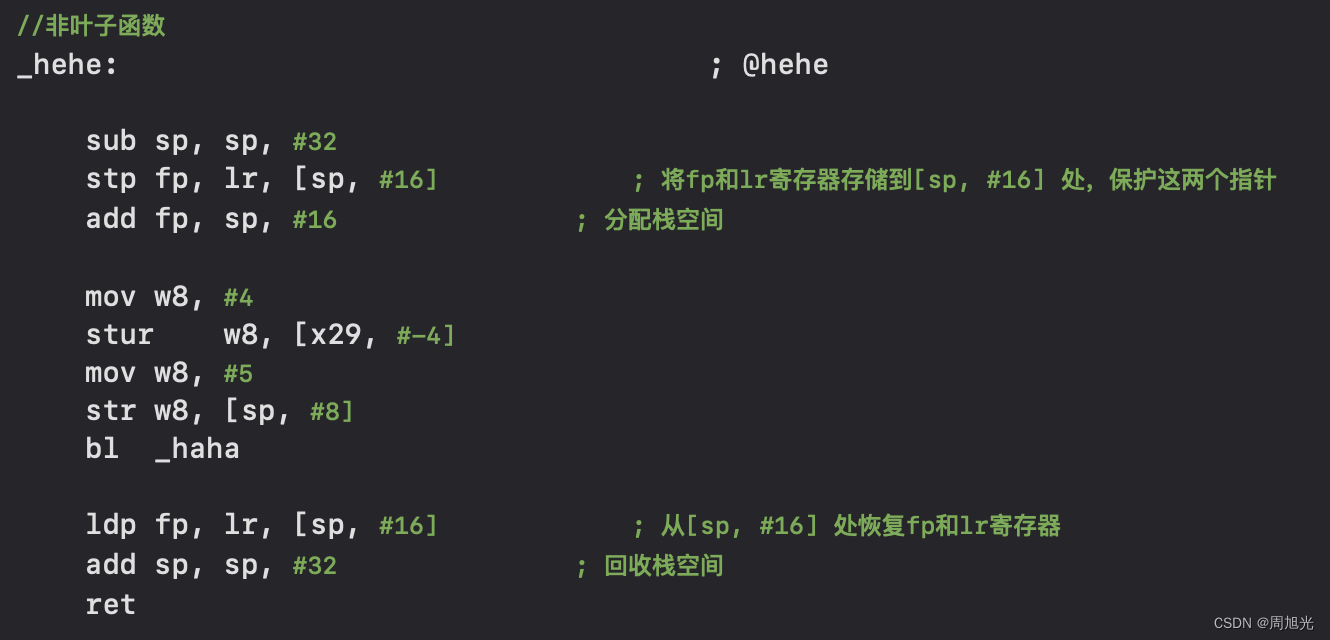

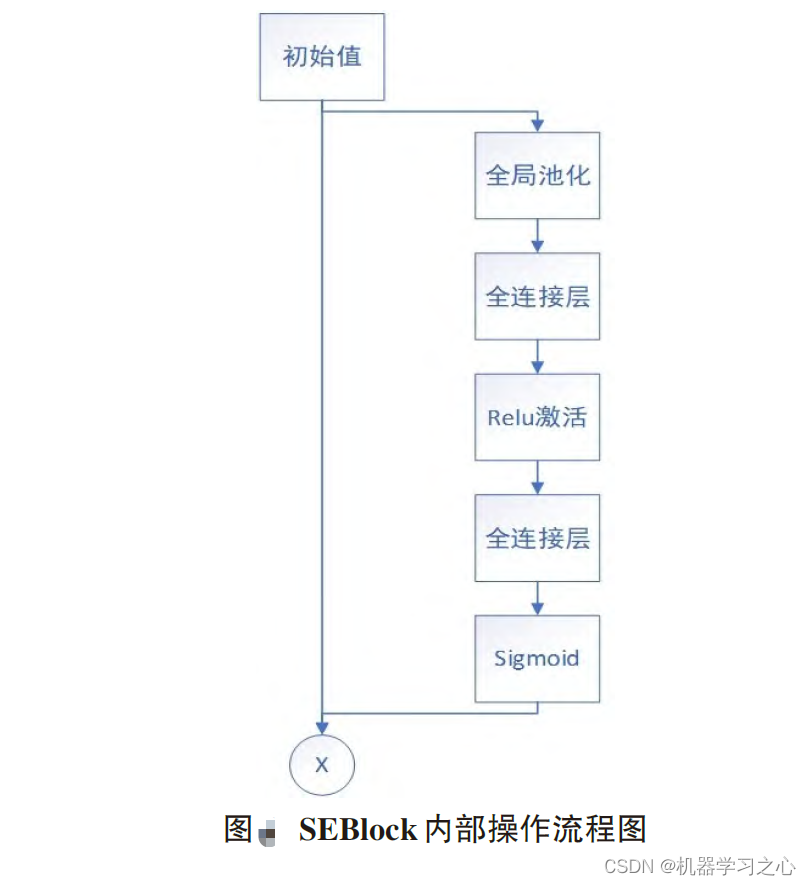

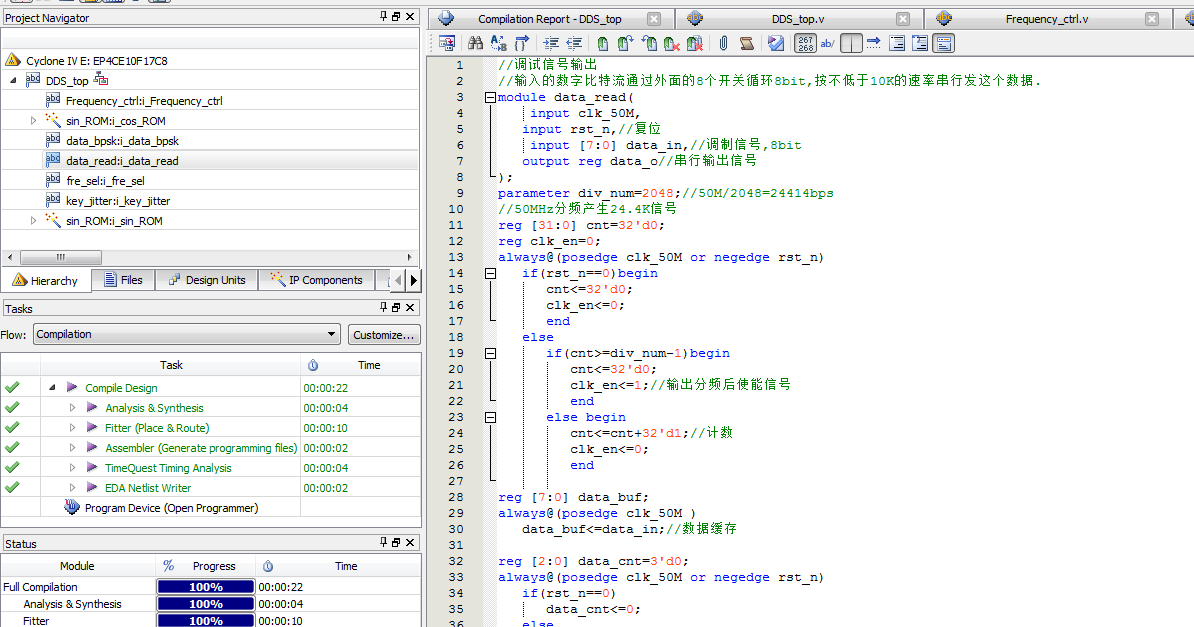

首先需要产生调制信号,调制信号使用外部8位拨码开关控制,设计一个并转串模块将8位并行信号转换为串行输出信号,信号比特流的速率不低于10kbps。然后需要设计载波信号,载波采用正弦波,使用ROM存储一个1024点的正弦波信号和余弦信号,同时为了使载波频率可调,通过一个按键控制ROM的读速率即可控制载波频率。最后设计调制模块,通过调制信号控制当前输出是正弦波还是余弦波,从而达到BPSK调制的目的。

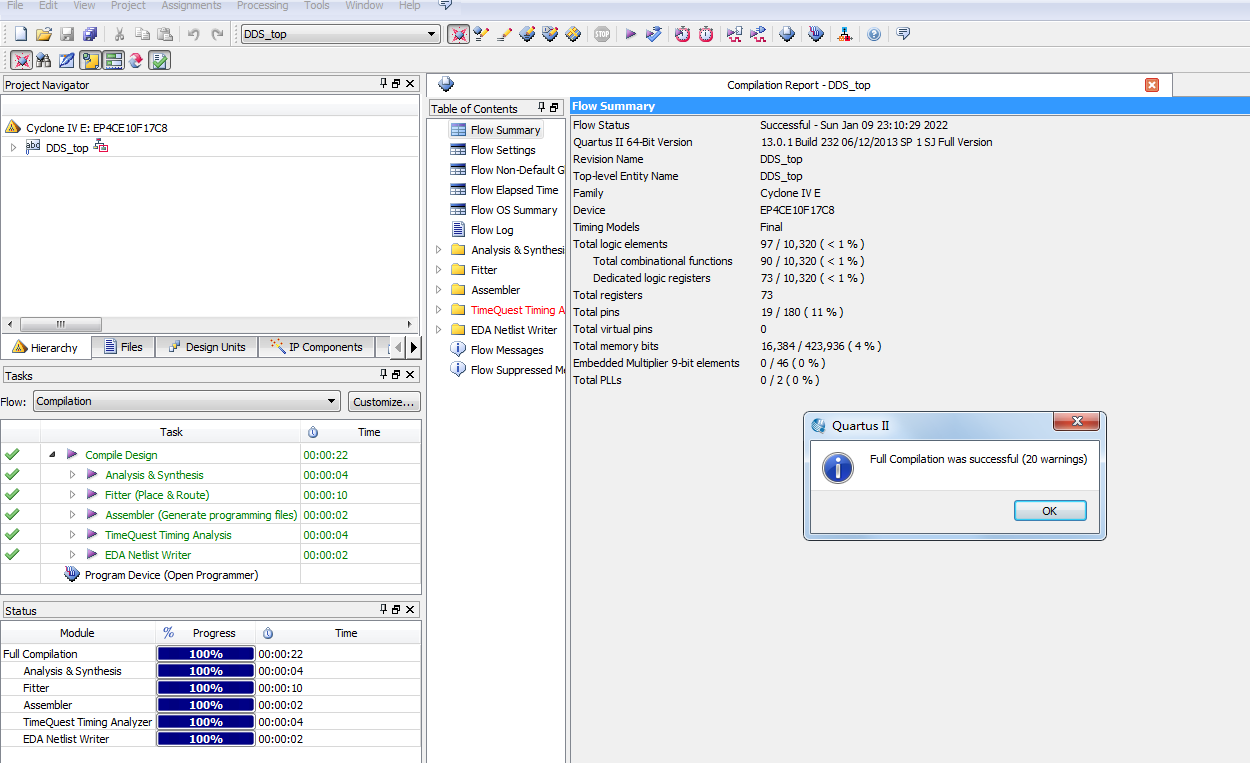

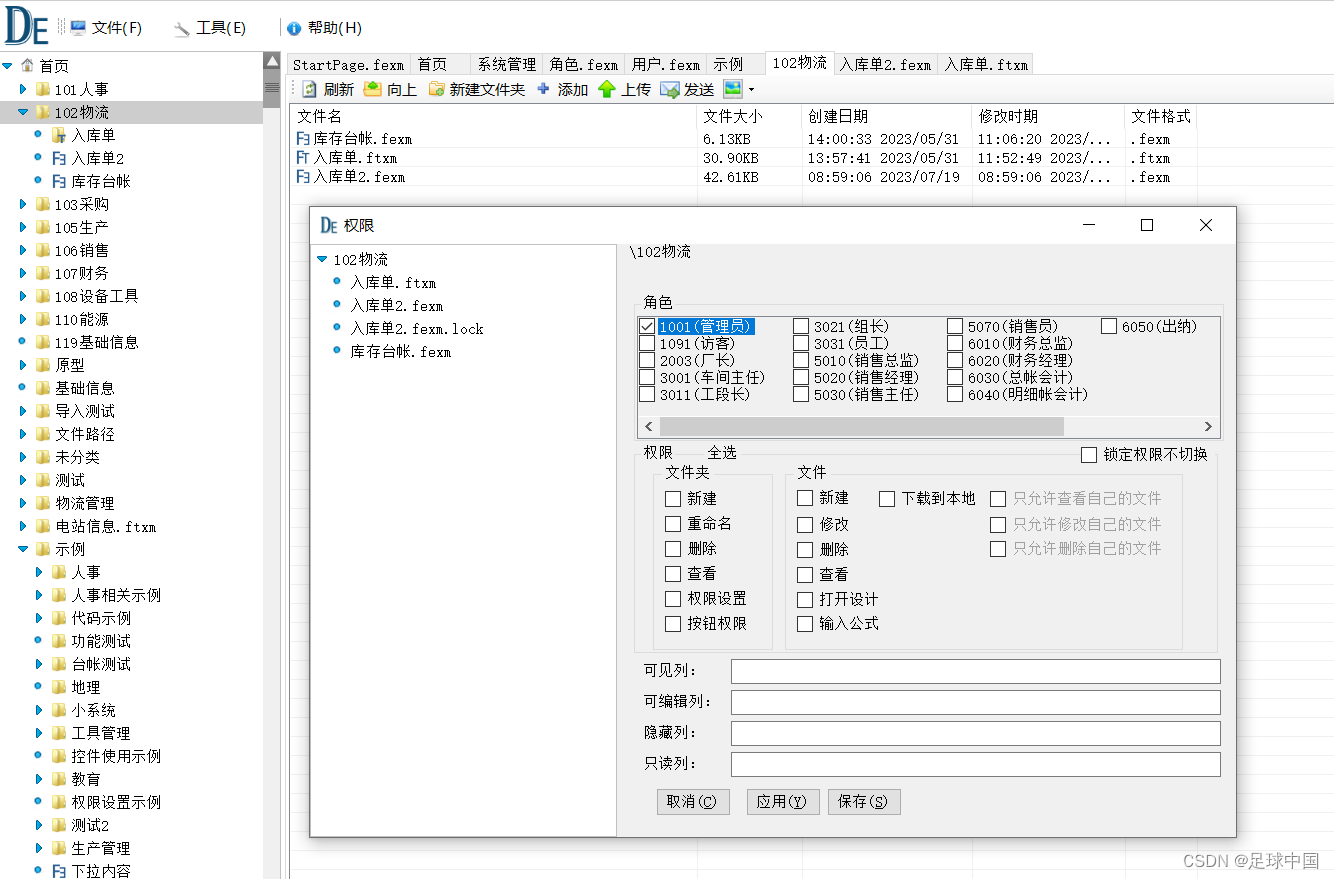

1. 工程文件

2. 程序文件

3. 程序编译

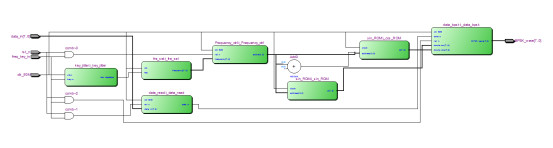

4. RTL图

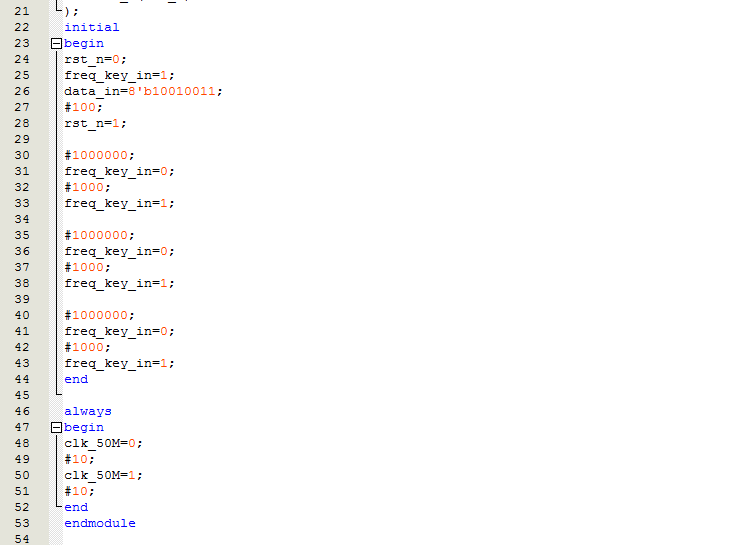

5. Testbench

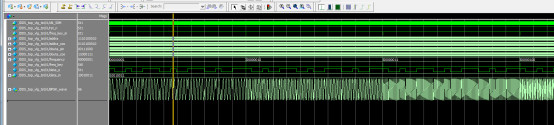

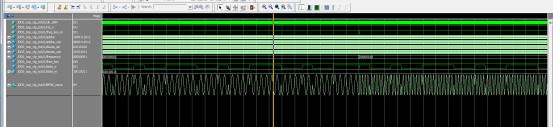

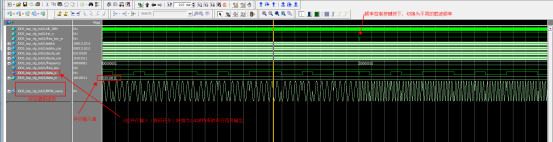

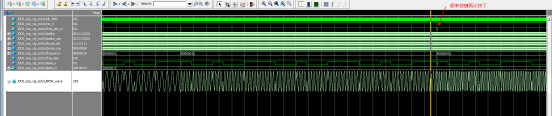

6. 仿真图

![[JAVAee]SpringBoot日志文件](https://img-blog.csdnimg.cn/509ae6ef9c8e42468a2950507020fc85.png)