问题

逻辑工程师vivado工具生成的pl hdf文件后,通过xilinx的工具解析的的dts文件,会出现中断号异常的问题。

原始问题肯定是硬件表现为通讯异常,此处以网口为例,则网口不通。

网口查询

uboot下网口信息

如下命令查询到 两个mac下对应的phy,地址分别为4和6,和硬件设计一致。

> mdio list

ethernet@e0047000:

4 - Generic PHY <--> ethernet@e0047000

6 - Generic PHY <--> ethernet@e0049000

ethernet@e0049000:在线更新uboot

sf probe 0:0 && tftp 0x1000000 BOOT.bin

sf update 0x1000000 0 0xc6fc0linux 下面读取phy寄存器

例如工作模式确认

# mdio eth0 0x1e 0xa001;mdio eth0 0x1f

write phy addr: 0x4 reg: 0x1e value : 0xa001read phy addr: 0x4 reg: 0x1f value : 0x8160#

#

# mdio eth2 0x1e 0xa001;mdio eth2 0x1f

write phy addr: 0x4 reg: 0x1e value : 0xa001read phy addr: 0x4 reg: 0x1f value : 0x8160uboot下对phy复位

PL 出的网口,连接的phy 由EMIO 9关键控制复位。

fmsh> gpio clear portc9

gpio: pin portc9 (gpio 63) value is 0

fmsh> gpio set portc9

gpio: pin portc9 (gpio 63) value is 1

Warning: value of pin is still 0

fmsh>PL中断

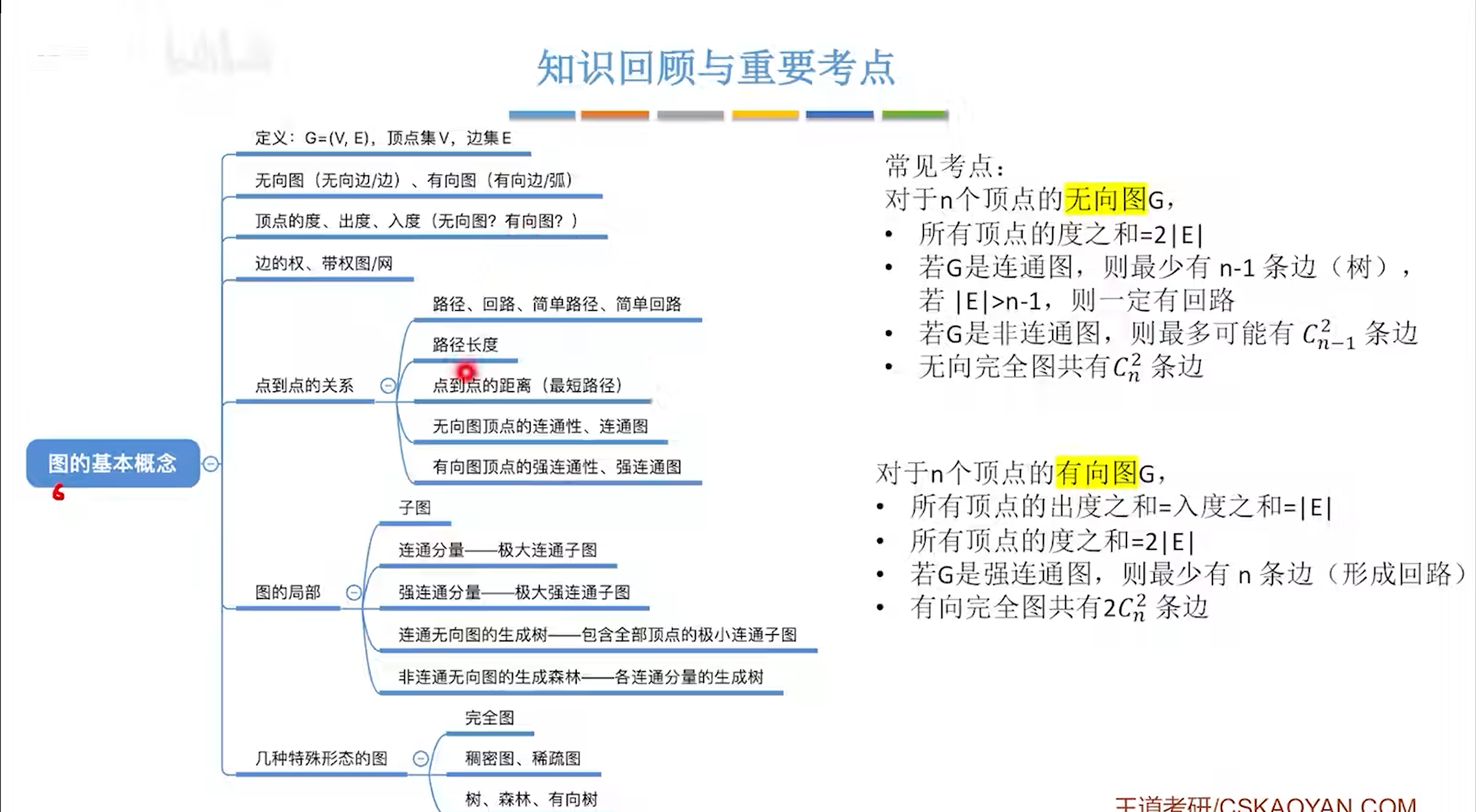

PS分配给PL的中断

PL 到PS的中断总共16个。分别为57-64以及84-91

中断号与逻辑设计

上面16个中断号与逻辑设计中的如下16个连接线是一一对应的。即逻辑功能连接到ln0时,对应的中断是57,依次类推。

例如 此处连接的ln9 ln10两个,则对应的中断为85与86两个。

连接线bug

如上图所示,注意到此处ln1 ln3 ln4是悬空的,这时候用vivado生成的中断号信息为31 32,即对应中断表中的63,64(前者加32),和设计是不对应的。

分析可以看出,当有中断悬空的时候,后续的管脚会自动上移动。

中断和设计不一致,导致中断一致收不到,进而异常。

连接线bug解决

xlconcat前面管脚不要悬空。

基于此,生成的dts文件中断部分可以直接使用,不需要单独修改。

dts 网络部分的中断会在上述中断表的基础上减32.

而串口部分则与中断表相同。这应该是驱动层的设计差异。