MIPI协议

- MIPI介绍

- 协议层

- 显示接口(Display)

- DBI(Display Bus Interface)

- 并行传输

- 串行传输

- DPI(Display Pixel Interface,也称RGB接口)

- DSI(Display Serial Interface)

- Application,即应用层

- lane manager层

- D-PHY物理层

- STM32 MCU支持的显示接口类型

- 相机&图像接口(Camera)

- CSI(Camera Serial Interface)

- 硬件层

- D-PHY

- 概述

- 物理层传输状态

- D-PHY三种模式

- 高速模式(Burst Mode)

- 控制模式(Control mode)

- 逃避模式(Escape mode)

- 三种模式的切换

- 从低功耗状态进入高速状态

- Turnaround 模式用于改变数据传输的方向

- 进入Escape Mode

- C-PHY

- Wire state(线状态)

- 工作模式

- A-PHY

- M-PHY

- MIPI时钟设置

MIPI介绍

MIPI联盟,即移动产业处理器接口(Mobile Industry Processor Interface 简称MIPI)联盟。是2003年由ARM,Nokia,ST,TI等公司成立的一个联盟,目的是把电子设备内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少电子设备设计的复杂程度和增加设计灵活性。统一接口标准的好处是电子设备厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

该组织主要定义了4种应用场景的协议:

- Multimedia:主要包含CSI(Camera Serial Interface,摄像头串行接口)、DSI(Display Serial Interface,显示串行接口)等属于重点介绍对象;还有soundwire、麦克风/喇叭接口SLIMbus。

- Control&Data:I3C

- Chip-to-Chip Inter Process Communications:射频接口DigRF

- Debug & Trace:

这个组织还有定义了其他接口:如battery interface等。

MIPI并不是一个单一的接口或协议,而是包含了一套协议和标准,MIPI协议主要包含三层,从下往上分别为:物理层、协议层、应用层。

如下图介绍了MIPI联盟的家族谱:

1、CSI-2、DSI-2 的物理层有A-PHY C-PHY D-PHY

2、CSI-3、UFS 的物理层是M-PHY

协议层

显示接口(Display)

DBI(Display Bus Interface)

DBI是MIPI联盟发布的第一个显示标准,用来规定显示接口。MIPI-DBI中定义了三类接口:

- A类:基于Motorola 6800总线

- B类:基于Intel 8080总线

- C类:基于SPI协议

DBI(Display Bus Interface), 显示总线接口, 也称MCU接口或者80/8080接口,DBI接口最大的特点就是LCM自带framebuffer, 存储Host端发过来的数据, 并由内部的控制IC不断重复的刷到LCD上, 也就是说其内部实现了自刷新, Host只要发送一次数据即可, 这帧数据会一直显示在屏幕上。由于不需要Host端自刷新,对Host处理器的要求很低, 没有时钟线,Host和LCM可以是简单的GPIO相连

DBI传输可以选择并口和串口传输,两者差别就是数据线数量不同,时序是相同的。

并行传输

并行传输一般包括以下信号线:

- CSX: 片选信号,图中低电平有效

- D/CX:数据/命令信号

- WRX: 写使能, 上升沿锁存

- RDX:读使能, 上升沿锁存

- D[17:0]: 数据线

M0~3四根引脚有0000、0001、0010、0011四种配置,分别对应8位、16位、9位、18位并行数据线

TE(tearing effect)引脚用于同步,可以指示LCM一帧数据是否刷完(也可配置LCM每刷多少帧产生一个信号告知Host)

以上信号线中,除数据线外,其它信号线表示的写或读的时序,具体的写或读的内容是通过数据信号线传输的,可以是命令或像素点值,命令又分为带参数和不带参数两种,带参数则均为两个字节。上面的M0-3配置了数据线的条数,每种配置根据信号线时序的不同,又分为四种:写数据或命令的参数、写命令、读数据、读命令的参数。具体的时序图如下:

以RGB565为例:先发送写内存命令0x2c, 接着开始写帧数据,即连续发送所有像素点的数据

并行传输接口可以用FSMC接口来实现,并且FSMC接口支持6800和8080两种模式

串行传输

串行传输则有三条线和四条线两种:

- 3线制时信号分时钟DCX、片选CSX、数据SDA,特别注意,3线制每传输一个字节需要9bit, 多出一个bit来表示该字节是命令还是数据,用GPIO实现相对较好,因为SPI的每字节只能是8位,即使指定spi->bits_per_word = 9,SPI也会将其自动转为读取两个字节。

- 4线制每byte就是8bit,通过这根多出的引脚告知LCM这个byte是命令还是数据。

DPI(Display Pixel Interface,也称RGB接口)

MIPI-DPI通过TFT控制器对接口进行标准化。用来与没有帧缓冲器的显示器进行连接。像素数据必须实时流式传输到显示器。

显示像素接口, 也称RGB接口, 之所以叫像素接口, 是因为数据采用并口在一个时钟周期就传输一个像素的数据, 所以时钟一般设置像素时钟而不是bit时钟。与DBI不同的是, LCD端没有framebuffer, 转移到Host端, 所以为了维持画面能够持续显示在屏幕上, Host要持续发送数据过去, 并且为保证数据的同步, 引入VSYNC/HSYNC等功能(更准确说是继承了以前的叫法),信号包括:

- Vsync:帧同步信号

- vbp: 帧同步信号的后肩,单位为1行的时间

- vfp: 帧同步信号的前肩,单位为1行的时间。

- Hsync:行同步信号

- hbp:行同步信号的后肩,单位为1像素的时间

- hfp:行同步信号的前肩,单位为1像素的时间

- Dotclk:点时钟或称像素时钟

- DE:数据有效信号(屏蔽掉前后肩)

但是这里特别注意的是,vbp/vfp/hbp/hfp这四个参数只是为了兼容以前的CRT显示器而保留的,而物理管脚上,这四个信号无论是CRT还是LED也不需要单独的管脚,它是用DE信号和Vsync、Hsync组合来实现这个四个参数的。

同时,DPI接口的数据管脚只传输数据,命令由单独的SPI接口来传输,所以典型的DPI控制器管脚包括:CS、RST、SCL、SDA、Vsync、Hsync、DOTCLK、DB(0-15),其中时钟是像素时钟,即一个象素点的16位或24位数据是在一个像素时钟内并型传输过去的

LCD显示需要显示控制器,显示控制器是LCD越来越大,功能越来越多的发展结果。 LCD控制器同LCD驱动器是有着本质区别的。简单来说LCD控制器在嵌入式系统中的功能如同显卡在计算机中所起到的作用。LCD控制器负责把显存(可能是内存中的指定域)中的LCD图形数据传输到LCD驱动器(LCD driver)上,并产生必须的LCD控制信号,从而控制和完成图形的显示,翻转,叠加,缩放等一系列复杂的图形显示功能。LCD驱动器则只负责把CPU发送的图像数据在LCD显示出来,不会对图像做任何的处理。LCD控制器可以兼容各种各样的CPU接口以及各种各样的LCD模块的接口,硬件完成复杂图像显示功能(缩放,翻转,叠加,动态等等)

LCD控制器的功能就是生成LCD像素时钟,将GRAM中的数据搬运到LCD屏幕上去显示。在一般的小型LCD模块一般都集成了一个LCD控制器,如常用的ili9320/ili9325等型号,这些LCD模块同时还集成了几百KB大小的RAM,用于显示;一般地MCU先通过8080接口或SPI向控制器发送命令,配置LCD参数,然后向集成的RAM中写入数据就可以显示,是低成本项目的首选方案。

STM32F429自带的LTDC也是LCD控制器,与ili9320相比,支持的分辨率更高,功能更多,但是LTDC只负责产生LCD需要的时序,并没有集成RAM。那么在使用LTDC的时候,首先要配置LCD的时序,然后要设置GRAM的地址(这里GRAM的地址就是外扩的SDRAM的地址),最后开启LTDC。配置好LTDC之后,硬件会自动将GRAM中的内容搬运到LCD屏幕上,只要改变GRAM中的数据就可以改变显示内容。

LTDC支持2个图层和1个背景图层,一般情况下用一个图层显示就可以了;这2个图层可以单独设置显示区域和GRAM地址,并且同时开启时,硬件自动将2个图层的显示内容进行混合,混合顺序是:图层2 -> 图层1 -> 背景色,图层2位于最顶层

这里有一个理解起来比较困难的地方,就是LTDC和DMA2D之间的关系,因为从二者的逻辑图功能上看,似乎完全一样。先看逻辑图

从图上看,二者都有像素格式转换、图层混合、输出格式转换功能。其部件意义如下:

- FG FIFO 与 BG FIFO:是两个 64x32 位大小的缓冲区,它们用于缓存从 AHB总线获取的像素数据,分别专用于缓冲前景层和背景层的数据源。AHB总线的数据源一般是 SDRAM,也就是说在 LTDC外设中配置的前景层及背景层数据源地址一般指向 SDRAM 的存储空间,使用 SDRAM 的部分空间作为显存。

- FG PFC 与 BG PFC:是两个像素格式转换器,分别用于前景层和背景层的像素格式转换,不管从 FIFO 的数据源格式如何,都把它转化成字的格式(即 32 位),ARGB8888。图中的“ɑ”表示 Alpha,即透明度,经过 PFC,透明度会被扩展成 8 位的格式。图中的“CLUT”表示颜色查找表(Color Lookup Table),它使用一个 256x32 位的空间缓存 256 种颜色,颜色的格式是 ARGB8888 或RGB888。利用颜色查找表,实际的图像只使用这 256 种颜色,每种颜色4*8=32位。该数据并不是直接的 RGB 颜色数据,而是指向颜色查找表的地址偏移,即表示这个像素点应该显示颜色查找表中的哪一种颜色。DMA2D 的颜色查找表可以由 CPU自动加载或编程手动加载。

- 混合器:FIFO 中的数据源经过 PFC像素格式转换器后,前景层和背景层的图像都输入到混合器中运算,运算公式如下:

- OUT PFC:输出像素格式转换器,它把混合器转换得到的图像转换成目标格式,如ARGB8888、RGB888、RGB565、ARGB1555 或 ARGB4444,具体的格式可根据需要在输出 PFC控制寄存器 DMA2D_OPFCCR 中选择。STM32F429 芯片使用 LTDC、DMA2D 及 RAM 存储器,构成了一个完整的液晶控制器。

要理解上述功能上的看似重复,索性从头学习一下DMA,stm32有两个DMA控制器,DMA1有7个DMA通道,DMA2有5个通道。stm32增加一个专用于图形加带的DMA2D,就是我们上边介绍的。每个外设可以使用的DMA通道是不同的。如下表:

在传统的DMA传输中,有如下特点:

1、只能单纯的完成四种类型传输(外设到内存、内存到外设、内存到内存、外设到外设),不能像DMA2D那种做各种数据的变换

2、使用方法是在初始化程序中完成设置,然后启动DMA。设置主要涉及源地址、目标地址、传输数据量这三个。DMA控制器传输的终点就是剩余传输数据量为0(循环传输不是这样的)。换句话说只要剩余传输数据量不是0,而且DMA是启动状态,那么就会发生数据传输。

在stm32cube中配置DMA通道,只涉及add一条通道,并没有以上源地址等配置工作,可见,DMA初始化的每一步只是设置一条DMA通道相关的配置参数,而具体的源地址、目标地址、传输数据量、数据格式等参数是DMA请求源在启动DMA前在代码中设置的。

DMA2D是专用于图形加速的DMA,在stm32cube中只需要激活即可,然后设置相关的参数,同样没有源地址等设置。应当也是在初始化代码中设置的。

DMA2D有四种工作模式,在stm32f769的LCD例程中设置为M-M,即内存到内存,从表中可以看到,这种模式只把LTDC设置的SDRAM缓存中的数据传入FIFO,并不执行上述DMA2D框图中的PFC及混合功能,而是直接输出到OUT FIFO,而这个地址应当就是设置为LTDC控制器的FIFO。

那么,即然指定M_M模式不启用PFC及混合等功能,那和DMA传输有何不同呢?在stm32cube配置中可以看到,专用于图形传输的DMA2D可以设置输入数据的格式,如ARGB8888,还有A通道混合等设置参数。

所以综上,DMA2D完成的是从显示缓存到LDTC的FIFO的数据运输关系,存于DMA2D可能不仅只为LDTC服务,因此,DMA2D同样有图像格式转换及混合等功能,但是在它为LDTC服务时,LDTC本身具有这些功能,所以只启用DMA2D的内存到内存模式的搬运功能。

顺便介绍两个概念:帧数(帧率)和刷新率:

1)帧率:就是画面改变的速度,帧数高画面就流畅。理论上,每一帧都是不同的画面。60fps就是每秒钟显卡生成60张画面图片。

2)刷新率:显示信号输出刷新的速度。60赫兹(hertz)就是每秒钟显卡向显示器输出60次信号。

假设帧数是刷新率的1/2,即显卡每两次向显示器输出的画面是用一幅画面。相反,如果帧数是刷新率的2倍,那么画面每改变两次,其中只有1次是被显卡发送并在显示器上显示的。 所以高于刷新率的帧数都是无效帧数,对画面效果没有任何提升,反而可能导致画面异常。

STM32F429 系列芯片内部自带一个 LTDC液晶控制器,使用 SDRAM 的部分空间作为显存,可直接控制液晶面板,无需额外增加液晶控制器芯片。STM32 的 LTDC液晶控制器最高支持 800x600 分辨率的屏幕;可支持多种颜色格式,包括 RGB888、RGB565、ARGB8888 和 ARGB1555 等(其中的“A”是指透明像素);支持 2 层显示数据混合,利用这个特性,可高效地做出背景和前景分离的显示效果,如以视频为背景,在前景显示弹幕。

LTDC外设使用 3 种时钟信号,包括 AHB时钟、APB2 时钟及像素时钟 LCD_CLK。AHB时钟用于驱动数据从存储器存储到 FIFO,APB2 时钟用于驱动 LTDC 的寄存器。而LCD_CLK 用于生成与液晶面板通讯的同步时钟。

LCD_CLK的来源是 HSE(高速外部晶振),经过“/M”分频因子分频输出到“PLLSAI”分频器,再经倍频因子 N 倍频得到“PLLSAIN”时钟、再由“/R”因子分频得到“PLLCDCLK”时钟,再经过“DIV”因子得到“LCD-TFT clock”,“LCD-TFT clock”即通讯中的同步时钟LCD_CLK,它使用 LCD_CLK 引脚输出。

在实际使用 LTDC控制器控制液晶屏时,使 LTDC正常工作后,往配置好的显存地址写入要显示的像素数据,LTDC 就会把这些数据从显存搬运到液晶面板进行显示,而显示数据的容量非常大,所以我们希望能用 DMA来操作,针对这个需求,STM32 专门定制了DMA2D 外设,它可用于快速绘制矩形、直线、分层数据混合、数据复制以及进行图像数据格式转换,可以把它理解为图形专用的 DMA。

DPI模式需要MCU带有LTDC控制器,以stm32f429为例 ,其内部LTDC框图如下:LTDC利用简单的3.3V信号提供了多达28个信号,包括: • 像素时钟LCD_CLK。 • 数据使能LCD_DE。 • 同步信号(LCD_HSYNC和LCD_VSYNC)。 • 像素数据RGB888。

LTDC控制器只能驱动上述的信号, 不属于LTDC的信号可以使用GPIO和其他外设进行管理。 比如背光单元需要额外的背光控制电路和GPIO。 一些显示面板需要复位信号以及串行接口(如I2C或SPI)。这些接口通常用于显示器初始 化命令或触摸面板控制。

LTDC可以按照以下并行格式输出数据:RGB565、RGB666和RGB888。LTDC信号极性可编程 LTDC控制信号的极性是可编程的,这使得STM32微控制器能够驱动任意RGB并行显示器。利 用LTDC_GCR寄存器,可以将控制信号(Hsync, Vsync和数据使能DE)以及像素时钟 (LCD_CLK)定义为高电平有效或低电平有效。

DPI方式显示的整个流程是MCU先生成数据,放入缓存,该缓存大小是根据LCD屏像素大小来决定的,如果MCU内部RAM够用,则可以将缓存放在MCU内部RAM中,如果内部RAM不足,则放在FMC接口的外部RAM中。内部RAM的带宽大,无延时。据有文章称,stm32f429将缓外放在外部的SDRAM缓冲区时,当时钟高于40Mhz时,就无法正常显示。

微控制器对要在帧缓冲器中显示的图像进行计算,以组成图标或图像等图形基元。CPU通过运行图形库软件来执行此过程。该过程可以由图形库使用专用硬件(如DMA2DChrom-Art Accelerator®)来加速。帧缓冲器更新的频率越高,动画越流畅(动画每秒帧数)。双缓冲使用两个帧缓冲器,一个用于显示,一个用于存入下一帧,可以避免显示正在写入缓冲器的内容。显示控制器持续“刷新”显示器,以每秒60次(60Hz)的速度将帧缓冲器内容传送到显示屏。显示控制器可以嵌入显示模块或MCU中,即LTDC。

LTDC是以逐行方式读取图像数据的控制器。其存储器访问模式的长度为64字节,但当到达一行的结尾并且剩余数据少于64个字节时,LTDC将提取剩余的数据。

在每个像素时钟上升沿或时钟下降沿,并在屏幕有效区域内,LTDC层从其FIFO中检索一个 像素数据,将其转换为内部ARGB8888像素格式,并将其与背景和/或其他图层像素颜色进 行混合。得到的像素以RGB888格式编码,通过抖动单元并被驱动到RGB接口中。像素便会显示到屏幕上。

DSI(Display Serial Interface)

以上的DBI和DPI在速度上无法满足越来越大的带宽需求,而且不同的外设相应的硬件接口也不统一,由此就产生了MIPI-DSI接口,MIPI-DSI接口相对于上述接口主要完成了两个工作:

- 物理上在高速模式时采用200mV的差分信号传输,使单通道的信号传输速度最高达到1G

- 将传输分为四个层,上层对数据及命令进行协议打包,底层物理层只负责无差异的单bit信号传输,这些信号可以通过1-4个通道传,不再关心具体信号代表的意思,其含义转而由接收端上层按协议进行数据包的组装及命令解释,这样使得不同硬件可以使用相同的物理接口来和CPU连接,使硬件和接口各自独立。

MIPI_DSI封装了DBI或DPI信号,采用高带宽多通道差分链路,它使用标准的MIPI D-PHY作为物理链路。DSI分为DSI、DSI-2,没有DSI-1。

注意:

- 1、DSI协议已经发展到了V1.3版本,其实截止到2024.7.4,是到了V1.3.2版本

- 2、DSI协议的物理层只有D-PHY

- 3、DSI-2协议其实已经发展到了V2.1版本(截止2024.7.4),并支持MIPI C-PHY v2.0/v2.1 和 MIPI D-PHY v3.0的物理层

从整体流程上看到,DBI、DPI都是相应的控制器将数据发给LCD,而DSI用的是LTDC产生的数据,LTDC通过内部DBI接口将数据传给SDIHOST,然后才开始下面四层DSI接口协议的处理封包。所有说DSI是封装了DBI或DPI。与配置DSI时,一定会配置相应的LTDC

Application,即应用层

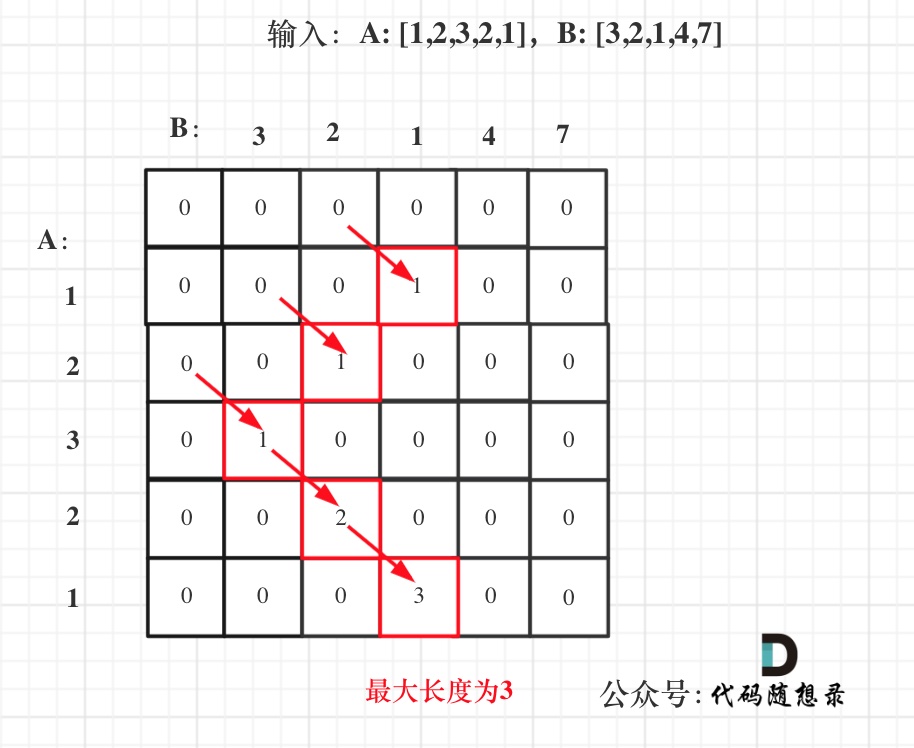

MIPI定义的最上层是Application,即应用层,可由软件或者硬件实现。它的作用是把像素值或命令打包了8位的字节包,而且整个MIPI从最上层到最下层的物理层,发送单元都是按一个字节来发送的。每一种图像的像素格式是不同的,除了RAW8和JPEG8等几种外,其它的如RAW10、YUV422、RGB565、RGB555、RGB444的每个像素点的位数均不一样,Application层要按照各种格式的协议把每个像素点的各位分别打包成一个或多个字节。比如RGB565,一个像素点是16位,打包时会分成两个包,第一个是G2-4和B3-7共8位,第二个包是R3-7和G5-7共8位,同时注意,可能是最后24位的原因,不足24位的格式是使用高位的,所以本例是G的6位是2-7,没有0和1。

需指出,包有命令包、数据包,还有行同步、帧同步等功能包,长短包的字节数也不同,而不同格式的图像打包的方式也不同,那接收方怎么知道包的长度以及该怎么还原成正确的格式呢?这就是下面介绍的包格式中都含有的ID字节的作用了。无论长包还是短包,其发送都以SOT开始,收到SOT后,表示后边紧跟着的就是数据包,而第一个字节就是标识ID,数据标识(DI)字节的高两个bit定义了数据lane个数,后六个bit定义了执行类型。根据该执行类型就可以解析出包长度,包类型(如行同步,帧同步,命令包等),数据格式(8位、16位、24位,YUV,RGB等)

MIPI协议用这6位bit一共定义了33种字节类型,比如:帧开始,传输结束EOT,24位RGB格式等。所以包类型如下:

- 0x01 ( 000001 ) 表示本包是帧起始包,是一个短包 (SyncEvent, V Sync Start Short)

- 0x11 (010001 ) SyncEvent, V Sync End Short

- 0x21 100001 SyncEvent, H Sync Start Short

- 0x31 110001 SyncEvent, H Sync End Short

- 0x08 001000 Endof Transmission packet (EoTp) Short

- 0x02 000010 ColorMode (CM) Off Command Short

- 0x12 010010 ColorMode (CM) On Command Short

- 0x22 100010 ShutDown Peripheral Command Short

- 0x32 110010 TurnOn Peripheral Command Short

- 0x03 000011 GenericShort WRITE, no parameters Short

- 0x13 010011 GenericShort WRITE, 1 parameter Short

- 0x23 100011 GenericShort WRITE, 2 parameters Short

- 0x04 000100 GenericREAD, no parameters Short

- 0x14 010100 GenericREAD, 1 parameter Short

- 0x24 100100 GenericREAD, 2 parameters Short

- 0x05 000101 DCSShort WRITE, no parameters Short

- 0x15 010101 DCSShort WRITE, 1 parameter Short

- 0x06 000110 DCSREAD, no parameters Short

- 0x37 110111 SetMaximum Return Packet Size Short

- 0x09 001001 NullPacket, no data Long

- 0x19 011001 BlankingPacket, no data Long

- 0x29 101001 GenericLong Write Long

- 0x39 111001 DCSLong Write/write_LUT Command Packet Long

- 0x0C 001100 LooselyPacked Pixel Stream, 20-bit YCbCr, 4:2:2 Format Long

- 0x1C 011100 PackedPixel Stream, 24-bit YCbCr, 4:2:2 Format Long

- 0x2C 101100 PackedPixel Stream, 16-bit YCbCr, 4:2:2 Format Long

- 0x0D 001101 PackedPixel Stream, 30-bit RGB, 10-10-10 Format Long

- 0x1D 011101 PackedPixel Stream, 36-bit RGB, 12-12-12 Format Long

- 0x3D 111101 PackedPixel Stream, 12-bit YCbCr, 4:2:0 Format Long

- 0x0E 001110 PackedPixel Stream, 16-bit RGB, 5-6-5 Format Long

- 0x1E 011110 PackedPixel Stream, 18-bit RGB, 6-6-6 Format Long

- 0x2E 101110 LooselyPacked Pixel Stream, 18-bit RGB, 6-6-6 Format Long

- 0x3E 111110 PackedPixel Stream, 24-bit RGB, 8-8-8 Format Long

这些数据类型有的只能用于command模式,有的只能用于video模式,如下表,将一张图片写入LCD屏,如果用command DCS模式,则数据包ID类型为39h,如果用video长包,则数据包ID类型为3Eh。

另外,在下表中的数据类型中,有几类是指示数据包为指令包,它们分别是03h、13h、23h、05h、15h、06h、29h、39h,这些指令可以分为两大类:Generic类和DCS类,其中它们相应的指令基本是可以相互替代的,比如03h是无参数Generic短指令包,其功能和05h一样。它们之间的区别是DCS指令包中携带的指令是MIPI协议中的DCS标准指令,据说是nokia制定的。而Generic指令包中携带的指令即是各手机厂家自已制定的指令,比如苹果、华为都有自已的指令包,他们只要保证定制的MIPI和LCD能够互相解释该指令就可以,但是和不包含这些专用指令的硬件之间是无法通讯的。另外,根据下面介绍的数据包的格式,指令内容就是跟在ID字节后的,指令分为无参数、一个参数、二个参数三种。具体的DCS指令参见下面第二张表

下面会介绍整个数据包的结构,在数据包结构中会看到,除了数据本身各字节外,还是ECC包头检验字节和checksum结尾和校验字节,这部分是low level protocol层打包。而开始标志SOT和结束标志则是由最低层的物理层D-PHY打包的

lane manager层

在low level protocol下还有lane manager通道管理层,经过low level protocol层打包后的数据已经完全和上层分离,是不代表任何意思的纯字节数据,lane manager负责将这些字节流按规定的规则分配到通道中去发送。

在low level protocol层下就是负责具体发送和接收的物理层D-PHY,这部分在下面介绍完包格式后介绍。

下面介绍MIPI的最终完成的包的格式,包分为短包和长包,格式分别下:

- 短包(4 bytes长度)——命令设置或参数配置或同步信号传输,组成如下:标识(DI)- 1个字节、帧数据- 2个字节、错误检测(ECC)1个字节

- 长包——长包用2个字节定义数据长度,最多传输数据为65535,组成如下:

(1)帧头:4字节,组成和短包的4字节相同,区别是短包中2字节的帧数据是即内容,而长包中这2个字节是后面帧数据的长度

(2)帧数据:长度为0-65525个字节

(3)帧尾:2字节校验和

以上所有超过1字节的部分,发送时均是先发低字节。而每个字节内部,也是先发低位,再发高位。

D-PHY物理层

MIPI的D-PHY包含一个时钟通道和1-4个数据通道,每个通道包含的模块数是不同的,最多为5个模块,分别是:

- LP-TX:低功耗发送

- LP-RX:低功耗接收

- HS-TX:高速发送

- HS-RX:高速接收

- LP-CD:方向仲裁

需说明的是,无论一个通道含有上述5个模块中的几个,他们使用的均是同一对差分线Dp,Dn线,即这5个模块并不是同时工作的,要么工作在高速,要么工作是低速,要么工作在读,要么工作在写。一个通道中倒底应该包含几个模块,是这么确定的:

1、首先,只有双向通道才会用到LP-CD模块,如果是单向通道,即只读或只写,那么就不会有该模块。而时钟信号只能是主机发出,所以时钟通道肯定不会有该模块。同时,MIPI DSI有两种工作模式,分别是command模式和vedio模式,这两种模式对上面的显示接口类似,分别针对LCD中有显存和没显存的情况。 在command模式,数据lane 0应是双向的;其他的数据lane应是单向的,在vedio模式,数据lane0可以是双向或单向的;其他的数据通道必须是单向的。Master低功率传输仅采用lane0,外设接收在数据lane0只能使用低功耗模式。

2、CSI协议通常是不需要LP-CD模块。

3、综上所述,也就是说,D-PHY中一共有三种Lane,Unidirectional Clock Lane 、Unidirectional Data Lane以及Bi-directional Data Lane。

单个通道的结构图如下:

STM32 MCU支持的显示接口类型

- 1、所有STM32 MCU均支持MIPI-DBI C类(SPI)接口

- 2、带F(S)MC的所有STM32 MCU均支持MIPI-DBI A类和B类接口,即将LCD当存内存一样接在FSMC接口上

- 3、带LTDC的STM32 MCU支持MIPI-DPI接口

- 4、嵌入DSI主机的STM32 MCU支持MIPI-DSI接口

大致来说,103等可以采用FSMC接口,429等可以采样LTDC RGB模式,469、769等可以使用DSI模式。几种模式的整体流程图如下:

相机&图像接口(Camera)

CSI(Camera Serial Interface)

CSI(Camera Serial Interface)是由MIPI联盟下Camera工作组指定的接口标准。CSI-2是MIPI CSI第二版,CSI-3是MIPI CSI第二版。主要由应用层、协议层、物理层组成,最大支持4通道数据传输、单线传输速度高达1Gb/s。

注意:

- 1、上面的“2”与“3” 准确的来说不是版本号,而是代表协议类型;

- 2、根据官网信息,CSI-3使用M-PHY作为物理层,以后用到后补充;

- 3、没有CSI-1

CSI-2的演化版本见下图:

注意:

- 1、CSI-2当前共有V1.1 V1.2 V1.3 V2.0 V2.1 V3.0 V4.0共七个版本,截止2024.7.4 已有V4.0.1、V4.1一共9个版本

- 2、不同的版本其物理层不一样,也就意味着硬件接口会根据物理层的不同有差异;其物理层版本也不一样,也即单lane速率也不一样

- 3、MIPI不同物理层不同版本的单lane速率,是选择接口的重要依据(计算速率),后续补充如何计算

硬件层

MIPI的硬件也就是物理层,目前有D-PHY、M-PHY、C-PHY、A-PHY四种

- 2007年出现了D-PHY。

- 2008年提出了M-PHY。数据传输量最大,但在实际应用案例几乎没有。主要原因是和camera的应用发展有关,camera在达到20M的像素之后并没有像MIPI组织的预期一样继续大幅往上更高像素数方面发展。而M-PHY设备开发过于复杂,没有设备商支持,所以仍使用D-PHY协议。

- 2013年提出了C-PHY协议。相比M-PHY 传输速度低,但是和D-PHY更容易兼容,且设备开发成本较低。

- 2020年9月提出了A-PHY v1.0。主要解决长距离和可靠性问题。未来主要应用于车载场景。

D-PHY

概述

D-PHY协议最多支持5个Lane(通道)(一个时钟Lane,4个数据Lane),最少需要两个Lane(一个时钟Lane,一个数据Lane)。每一个Lane有两根线,分别为P和N,信号以差分的方式传输,同一周期一个高 一个低。clock高低时都进行数据采样。Clock Lane是必不可少的,Data Lane的数量可以根据传输数据的吞吐率要求来选择。一个Lane的含义是一组差分信号。

- Clock 信号是单向信号,只能Master向Slave提供,永远不变。

- Data信号可以是单向信号,也可以是半双工信号,即可以反向传输。反向传输的本质其实是通过Master去读Slave里的数据。这种半双工的双向信号的数据传送,在反向传输数据的时候(Slave To Master),带宽只有正向传输(Master To Slave)的四分之一。

D-PHY采用1 Lane源同步的差分时钟和1/2/4 Lane差分数据线来进行数据传输,是一个高速、低功耗的源同步物理层,他具有高速、低功耗、低成本等特点;D-PHY有很多版本:

物理层传输状态

D- PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式:

- HS模式(差分信号100mV-300mV):高速模式,低压差分信号,功耗大,高速率(80M -1Gbps),同步传送,用于传输高速图像数据,信号幅值(100mv-300mv)

- LP模式(单信号0V~1.2V):低功耗模式,单端信号,功耗小,速率低(< 10Mbps) ,异步传输,主要用于传输控制命令,信号幅值(0-1.2V)

链路层的模式分为:Command模式和Video模式。链路层选择Command模式时,物理层可以为HS模式,也可以为LP模式;链路层选择Video模式时,物理层只能选择HS模式。 command mode通过TE pin来同步,video mode通过将v-sync及h-sync信号包含在数据包里发送给panel来做同步,和RGB不同的是RGB专门有v-sync以及h-sync PIN引脚,而video mode是v-sync及h-sync信号包。

但是不同的屏会有不同的要求,有的屏的部分命令要求只能以低功耗模式传输。

每个通道的两条差分线可以工作在高速传输或低功耗传输,其中高速传输是200mv差分信号,速度80Mbps ~ 1Gbps/Lane ,两根线的相对电平高低来来表示是0或1,即此时有两种状态。而低功耗传输不是差分信号每通道最高速率是10M,电压是0-1.2V,两根线的电平状态相互独立,则有四种电平组合LP11、LP10、LP01、LP00,其中0表示低电平,即0V。1表示高电平,即1.2V。所以,高速状态和低功耗状态合计有6种状态。

注意:

1、HS仅仅在高速数据传输中使用,LP模式则同时包含控制模式

2、HS模式下逻辑0为DP为低、DN为高;逻辑1为DP为高、DN为低;

- HS-0:表示High-Speed模式下,Dp那根线的数据是0,由于High-Speed是差分信号,那么Dn固然就是1

- HS-1:表示High-Speed 模式下, Dp那根线的数据是1,由于High-Speed是差分信号,那么Dn固然就是0

3、在Low-Power模式下,Lane的2根线是独立的,不代表差分信号,那么2根线就有4种表达方式:

- LP-00:表示在Low-Power模式下,Dp那根线的数据是0,Dn那根线的数据是0

- LP-01:表示在Low-Power模式下,Dp那根线的数据是0,Dn那根线的数据是1

- LP-10:表示在Low-Power模式下,Dp那根线的数据是1,Dn那根线的数据是0

- LP-11:表示在Low-Power模式下,Dp那根线的数据是1,Dn那根线的数据是1

4、HS模式下高电平为0.2V,LP模式下高电平为1.2V;

5、Clock Lane一般都是使用非连续时钟信号模式,每传输完一帧图像数据,都会从 HS 模式切换回到LP 模式,当需要传输下一帧图像数据时,再从 LP 模式进入 HS 模式

D-PHY在没有任务时总是处于低功耗状态LP11下,所以无论进入以上三种模式的哪一种,都是从LP11状态开始的,从表中看到,该状态表示停止态。在进行数据突发传输时,data lane就进入高速数据传输模式,结束高速数据传输后又进入Stop State(LP11)。

这里需要强调一个问题,D-PHY的传输有HS和LP两种 ,在HS模式下数据包一定以SOT开始包起始,以EOT结束包结束。而SOT和EOT包都是特理层产生的。而在后面的LP模式下发送命令的时序看到,LP模式下是没有SOT和EOT包的。另外,从MIPI DSI v1.02版本开始,在EoT之前加入了EoTp短包,用于表示HS模式传输即将结束。EoTp短包是在协议层产生,在上面介绍的数据包ID中可以找到EoTp包。

在stm32cube中DSIHOST–Data and Clock lanes–Flow control可以配置是否使能EoTp包,使能分为使能EoT发送、EoTp接收、CRC接收、ECC接收,可以看到除了EoT有发送和接收外,CRC和ECC都只有接收,接收指的是接收子机发来的包,而EoT、CRC、ECC短包都是在协议层生成和解释的,根据以下HS数据包的格式看到,无论是长包还是短包,都包含CRC、ECC字节,即这两个字节是数据包的标准字节,主机发送数据包时,一定是按数据包格式封装好的,所以设置时没有CRC、ECC字节的使能及关闭选项。

为了兼容以前的版本,可以选择使能或关闭EoTp短包,开启和关闭的时序对比图如下:

使能EoT,连续发送2个短包SP,1个长包lgP,看到多了1个EoTp的SP

D-PHY三种模式

控制模式(Control Mode)、Escape Mode、和高速模式(HS Mode),其中前两种模式都属于LP状态下的两种模式,高速模式属于HS状态, Escape Mode被定义为LP状态下的一种比较特殊的操作模式:

- Burst Mode:高速模式。

- Control Mode:低功耗模式下的控制模式。

- Escape Mode:低功耗模式下的逃避模式。

在正常的操作时,数据通道处于高速模式或者控制模式。Burst Mode和Escape Mode之间不可以直接来回切换,必须通过Control Mode进行中转,即Burst Mode ↔ Control Mode ↔ Escape Mode

高速模式(Burst Mode)

高速模式,是HS状态下的模式,用来传输图像。在高速模式下,通道状态是差分的0或者1,也就是线对内Dp比Dn高时,定义为1;Dp比Dn低时,定义为0。此时典型的线上电压为差分200MV。

控制模式(Control mode)

控制模式是LP状态下的一种模式。高电平典型幅值为1.2V,此时Dp和Dn上的信号不是差分信号而是相互独立的。当Dp为1.2V,Dn也为1.2V时,MIPI协议定义状态为LP11;当Dp为1.2V,Dn为0V时,定义状态为LP10,依此类推,控制模式下可以组成LP11,LP10,LP01,LP00四个不同的状态。

MIPI协议规定,将控制模式的4个不同状态组成不同时序,用来代表着将要进入或者退出某种模式。比如LP11-LP01-LP00序列后,进入高速模式。

逃避模式(Escape mode)

逃避模式是数据Lane在LP状态下的一种特殊操作。在这种模式下,可以使data lane进入一些额外的功能:LPDT(Low-Power states,低功耗数据传输模式),ULPS(Ultra-Low states,超低功耗模式),Trigger。在正向传输时,是肯定支持Escape Mode的,但反向时可以不支持。

三种模式的切换

进入HS、Control Mode、Escape Mode三种式是通过特定的电平序列来实现的。首先看总的转换图,然后分步解释

从低功耗状态进入高速状态

正常情况下,Data Lane处于High-Speed mode或者Control mode,Data Lane进入Burst模式,首先发送进入高速请求,表中可以看到是LP01,其次进入Bridge状态,即LP00,这个状态起名Bridge,大概也是因为从低功耗的0-1.2V电平过渡到高速的200mv电平,先进入0电平,好像一个电平桥一般。所以整个电平序列为LP-11—>LP01—>LP00,然后发送SOT开始标志码,然后接上面的数据长包或短包进行发送。发送结束后,发EOT结束包,然后电平回到LP11。从Control模式进入HS模式时的步骤是LP11→LP01→LP00→HS0→SoT(00011101)→HS→LP11

在进入HS发送数据时,时钟lane会以差分信号提供时钟,时钟信号有如下特征

- 1、它会在数据通道开始前,先从时钟低功耗状态进入时钟HS状态,进入的方式也是LP11-LP01-LP00

- 2、时钟在进入HS在状态后,首先会维持一段时间的HS0状态(即时钟差分0平电),然后正常时钟01交替信号,再过一段时间,数据通道才会进入HS状态。stm32cube设置DSIHOST中有一个PHY Timings参数,对应的就是下面时钟通道中的Tcld-pre,OTM8009A显示驱动芯片要求的T CLK_PRE 最小值为8UI(Unit Interval,对应一个lane byte clock )。演示例中设置参数为10。

- 3、时钟通道要到所有数据通道均退出HS在状态后,才会进入低功耗状态,而且进入前会先持续一段时间,再进入HS0持续一段时间,最后通过时钟LP11进入时钟低功耗状状,这个过程和上面进入的进程是对称的

下面是时钟进入HS的时序,前半部分是退出HS,后半部分是进入HS

实际波形图:

通道1黄色波形为P,通道2蓝色波形为N,从中可以明显地区分出帧、行以及数据的间隔。

多个帧间隔

图像帧间隔(33帧左右)及帧数据

HS到HS的LP过渡过程

Turnaround 模式用于改变数据传输的方向

主机到从机的传输速度和从机到主机的传输速度是可以不一样的。比如现在是正向传输 ,通过Link Turnaround流程 就变成了反相传输。Link Turnaround流程只能在Control Mode下才能进行。同时,正如上面所述,每个通道最多含有5个模块,但是不一定含有全部5个,只有双向通道才需要即包含HS-TX、LP-TX,又包含HS-RX、LP-RX,同时包含方向控制LP-CD模块。

Turnaround 模式改变传输方向的时序图如下,需做几点说明

- 1、主机申请变为从机,同样从LP11停止态开始,然后发低功耗申请LP10,但是整个转换申请共5个电平状态LP-11—>LP10—>LP00—> LP10—> LP00。当LP00保持Tta-sure时间后,原来的从机就知道自已的身份已转换为主机,而在此之前,线路电平都是由原主机驱动的

- 2、从机确认自已身分转换为主机后,驱动LP00保持Tta-get时间,然后驱动线路电平到LP10,原主机(现从机)收到信号后,代表已知道自已的身份已转换为从机

- 3、新主机再把线路电平驱动到LP11,通知现从机,全部身份转换过程完成。

进入Escape Mode

Data lane通过一系列进入Escape Mode的操作流程(LP-11→LP-10→LP-00→LP-01→LP-00)才能进入Escape Mode。只要最后的LP-00状态出现在data lane上,就进入Escape Mode了。如果在没有到最后的LP-00状态前,data lane上出现了LP11(LP-10→LP-11),则会退出进入Escape Mode流程。一旦进入Escape mode模式,发送方就会发送1个8-bit的输入命令,来代表其请求的操作。

下表就是一些可以发送的请求操作命令,比如发送8位1110_0001,就表示将进入低功耗数据传输模式,发送0001_1110 就表示将进入超低功耗状态。 需注意的是几下几点:

- 1、所有从Escape Mode模式进入的各种模式都是不需要时钟通道的,这些模式的时钟是由数据通道特殊的编码方式来获得的。具体的说,是就数据通道的DP和DN线异或而来,而DP和DN数电平是相等和不等两种状态交替出现的,即00或11–01或10–00或11-01或10,两线异或就出现了周其变化的时钟信号

- 2、进入Escape Mode模式的电平序列LP-11,LP-10,LP-00,LP-01,LP-00是半周期发送的,即每位点半个周期,而紧随其后的8位命令字符或数据字符是全周期的,即每个位占有一个周期。而且没有HS传输模式中的SOT开始包、EOT结束包

- 3、命令或数据位是在DN线上发送的,如果是0,则在每个时钟周期内内会产生电平跳变,高电平和低电平各占半个时钟周期。如果是1,则不会产生电平跳变,始终是低电平。而DP线电平则根据需要来定,方式和保持和DN线电平异或后产生周期的时钟信号

- 4、数据发送可能有间断,即无数据时段,这时DN和DP都保持0电平,相应的时钟信号也消失,维持在0电平

首先来看,进入Escape Mode模式后可以发送的命令表:

其次,以发送Reset-Trigger命令为例,来看相应的电平时序

再次,来看进入Escape Mode后发送Low-Power Data Transmission命令进入低功耗模式,然后以此模式来传输数据的时序

再次,进入Ultra-Low Power State 超低功耗状态 等方式和以上进入Low-Power Data Transmission的方法类似

C-PHY

C-PHY是一个A/B/C三线系统。它在三个信号上运行,三合一,时钟被嵌入到数据中,从而不需要单独的时钟通道。MIPI CPHY必须CDR(Clock and Data Recovery 物理层信道中没有直接传输CLK信号,需要从接收数据中恢复时钟频率和相位)。

C-PHY使用 3-Phase symbol encoding技术,每一个符号可以传输2.28bits数据。C-PHY复用了大部分D-PHY的标准,能和D-PHY在同一芯片中共存,可以做兼容,但是其数据编码技术和D-PHY有本质的区别,其特性如下:

- 使用三根线一组传输,而不是之前使用的差分对;

- 采用5进制传输,效率高于D-PHY的二进制,效率为原来的2.27倍;

- 没有时钟信号,由于使用了三根线,并且时钟编码到每一个symbol中,而且在每一个symbol boundary都有电压的跳变,时钟恢复也比较简单。

Wire state(线状态)

C-PHY接口不需要单独的时钟信号线,而是直接从传输的数据中进行提取,而为了很好的从数据中提取时钟信息,同一周期A、B、C三根信号线上的电平都不一样,三根线三种电平,按照排列组合,总共会有六种状态。

对于每一种状态,下一步的变化都有5种变化状态。

我们要传输的信息是被编码到wire state中的,上文已经介绍CPHY具有+x、-x、+y、-y、+z、-z 6种wire state,当信号处于其中一种状态时,只能往剩下的5中状态切换,不会保持不变,哪怕CPHY传输的数据流不变,信号本身也会一直变化,信息被编码到状态与状态切换之中,被称之为symbol编码,换句话说,一共只有6条路,你占了一条,接下来只能往剩下的5条路里走。所以是5进制。

现在我们使用的是五进制系统,比特/符号的最大理论数量是log2(5)=2.3219。 映射器功能的构建是为了使映射率尽可能接近而不超过该理论极限。此外,映射器必须在两个整数之间进行映射。选择比率16/7≈2.28是为了实现上述限制。

另一种描述方式是,映射器需要将16个二进制位映射到一定数量的C-PHY符号,但我们如何确定映射到多少个符号(S)?在并行接口上有2的16次方种组合,映射器输出端的组合是5的S次方 => 2的16次方,所以S = 7。

工作模式

同D-PHY一样,C-PHY也有LP(低功耗)和HS(高速)两种工作模式

波形图

应用电路

C-PHY/D-PHY组合IP

A-PHY

D-PHY , C-PHY,M-PHY都能够进行大数据量的物理传输,但是这个几个物理层协议都无法进行较长距离的传输,导致了在车载和物联网领域的使用障碍。A-PHY的设计是为了能跨过整个车辆距离提供数据传输物理层支持。其最大传输距离能够达到15米,而最大传输速度未来能达到甚至超过48Gbps,远远超过LVDS的1.5GPS。它将帮助汽车行业加速高级驾驶员辅助系统(ADAS),自动驾驶系统(ADS)和汽车环视系统的性能。这其中包括摄像头和车载信息娱乐(IVI)显示器。

A-PHY的关键技术优势包括:

1、非对称优化架构。A-PHY从头开始设计,用于从摄像机/传感器到ECU以及ECU到显示器的高速非对称传输,同时为命令和控制提供并发的低速双向通信。与其他/对称架构相比,优化的非对称架构可简化设计并降低成本。

2、简化系统集成并降低成本:对使用MIPI CSI-2和DSI-2的设备的原生支持,最终消除了对桥接IC的需求

3、远距离:15米连接距离;

4、高性能:5档速度(2,4,8 和16Gbps),未来48Gbps甚至更高;

5、端到端的功能安全:APHY+CSI2/DSI2可以支持ASILB~ASILD的功能安全;

6、高可靠性:超低的误码率PER,10^-19,可在车辆使用寿命内提供空前的性能

移动协议重用。在数十亿智能手机和物联网设备中成功部署后,MIPI协议已被充分证明可直接用于汽车。

7、纯硬件协议层。就像在使用D-PHY / C-PHY分层的移动应用程序中一样,A-PHY与CSI-2 / DSI-2协议层紧密耦合,因此基本上在仅具有硬件的协议层下运行,而无需软件干预。该体系结构与其他接口相比,后者具有更高的灵活性,并利用软件层来实现这种灵活性。

8、针对布线,成本和重量的优化架构。由于A-PHY的优化的非对称架构和硬件协议分层,A-PHY的实现可以满足优化的布线,成本和重量要求。随着电子组件及其接口电缆的数量在实现自主的道路上增加,这一点变得越来越重要。

9、其他协议的灵活链路层支持。MIPI Alliance希望与其他将其本机协议应用于汽车的组织合作。这包括VESA,它正在调整其DisplayPort协议规范以供汽车使用。为了适应这些不断发展的规范,A-PHY包括一个通用数据链路层,该层可容纳不同的协议适应层,并计划支持VESA的车载DisplayPort协议。

10、高EMC抗扰性。MIPI已投入大量资金来分析和测量恶劣的汽车频道,并得出结论,基于窄带干扰消除器(NBIC)和独特的PHY层重传方案(RTS)的体系结构可提供最强大的性能,特别是对于需要更长数据速率的应用距离。

目前由于 Soc和设备都没有支持A-PHY,多数场景是需要桥接芯片连接

将来,Soc和设备本地支持集成的A-PHY就可以直接连接

可以看到,A-PHY不是直接跨越式的替换现有的方案,而是通过兼容性的替代现有的SerDes桥接芯片,最后实现完全不用桥接芯片的最终方案。这样的好处是平稳过渡,有利于APHY的接受和推广。

M-PHY

MIPI M-PHY专为需要快速通信通道以支持高分辨率图像、高视频帧速率和大型显示器或存储器的数据密集型应用而设计。这是一款多功能PHY,能够为工程师提供可跨行业平台开发的配置选项和功能,以有效解决多个市场和用例。

MIPI M-PHY用作MIPI CSI-3,MIPI DigRF,MIPI LLI和MIPI UniPro协议的物理层。MIPI M-PHY支持这些原生MIPI联盟协议以及来自PC生态系统的协议,以提供允许移动设备和PC之间融合的技术桥梁。使用MIPI M-PHY的PC工业协议包括JEDEC的UFS,PCI-SIG的Mobile PCIexpress和USB IF的SuperSpeed Inter Chip(SSIC)。

MIPI M-PHY与MIPI UniPort-M接口中的MIPI UniPro传输层相结合,用于移动设备中的创新网络实现。

在M-PHY协议中本地端TX和对端RX采用差分线进行传输。

MIPI M-PHY还使设计人员能够灵活地使用光学介质来实现系统内的高速连接。光学实现可以被配置为数米长的物理连接,以支持诸如汽车这样大平台的设计。

MIPI时钟设置

以MIPI LCD屏为例:

时钟频率=(屏幕分辨率宽width+hsync+hfp+hbp)x ( 屏幕分辨率高height+vsync+vfp+vbp) x(RGB显示数据宽度) x 帧率/ (lane_num)/2

其中:lane_num----是数据通道数量,一个时钟内,几个lane是可以同时传输数据的。同时,除以2是因为根据mipi通讯协议,CLK_N、CLK_P这两根时钟线的上升沿/下降沿可以获取到数据,即每个时钟周期可以传输2bit数据

这里涉及到的时钟有:

1、位时钟,是传输一个bit对应时钟,或者更准确的说是2个bit的时钟,因为时钟是差分信号,时钟DP、DN交叉两次才是一个完整的时钟,而时钟DP和DN线的上升沿都会采样,所以实际是半个时钟就会发送一个bit

2、字节时钟,数据被分配到多个数据通道上传输,但是每个通道上的最小单位是字节,即字节0到data0上,字节1在data1上

3、像素时钟,在stm32cube的时钟配置图上,即LCD_TFT时钟

4、ESC Clock,低功耗模式下的时钟,最大19.2M

以上时钟的关系为:

1)字节时钟=位时钟/8

2)像素时钟=字节时钟*数据通道数/每像素字节数

DSI传输像素时钟计算举例:

假设:LCD的分辨率为600 x 1024,帧率为57 HZ。行同步、行前肩、行后肩、帧同步、帧前肩、帧后肩分别为24、100、60、2、22、10,则:一帧图像的数据量为:FRAME_BIT=(600+24+100+60) x (1024+2+22+10) x(24)=19907328 bit,一秒钟的数据量为:19907328 x 57 = 1134.717696 Mbps,所需的mipi时钟频率为:1134717696/2(lane)/2= 283.679424 Mhz,但是stm32F769最大时钟只能到62.5M,所以它支持不了这么大屏或是不能以57帧的速度来刷新。

LCD=TFT时钟树频率:计算方式 DSI通道速率通道数/位每像素,500Mbs2/24=41.6666,约等于41.7MHz。

在mipi command mode模式下还有一个重要的信号:TE pin,它是来作为同步的,它是LCD的驱动IC在完成一帧的刷新后,返回给CPU的一个反馈信号,告知CPU当前帧已经刷新完毕,可以送另一帧新数据过来了。以此保证CPU发送数据和LCD的刷新步调一致,防止切屏。TE信号还要和显示缓冲的更新相匹配,防止在LCD刷新显示时更新RAM显存产生切屏,所有通常TE选择为上升沿触发。当然,在TE信号所在的一个时钟周期无法完成全部显示更新,但是只要写内存的速度比LCD刷新的速度快,LCD刷新拿到的数据就可以保证是内存已完更新完的数据,就可以保证不产生新旧数据同在一屏的切屏现象

DSI时钟的设置一共涉及到4个时钟:

1、AHB时钟:使用HCLK,用于LTDC将数据从存储器传输到 FIFO 层

2、APB2 时钟:PCLK2,用于LTDC配置寄存器

3、DSI通道时钟:stm32的DSI每通道最大传输数率是500Mbit,每通道最小单位是字节,所以在时钟图上是dsi lane byte=500/8=62.5M

4、像素时钟:即时钟图上的LCD_TFT,它是pllsai1倍频分频而来。计算值应为62.5通道数2每字节8位/每像素24位=41.6M。由于时钟设及多个外设,所以在时钟图上配置这个时钟时最为麻烦,本来可以直接填入41.6,但是stm32cube会更多出现两种情况:

- 找不到合适的参数值

- 手工设置各倍频分频参数,结果会自动改回来到原值

可能要经过很多次尝试,才会将LCD_TFT成功的设置为41.6M,这可能是stm32cube的问题,最好的方式可能是先填入41.6自动计算,然后再填改HCLK、APB1等时钟到正确的值。