系列文章目录

PCIe扫盲(一)

PCIe扫盲(二)

PCIe扫盲(三)

PCIe扫盲(四)

PCIe扫盲(五)

PCIe扫盲(六)

PCIe扫盲(七)

PCIe扫盲(八)

PCIe扫盲(九)

文章目录

- 系列文章目录

- 物理层电气部分基础(一)

- L0 模式下的链路结构图(状态图)如下:

- L0s 模式下的链路结构图(状态图)如下:

- L1 模式下的链路结构图(状态图)如下:

- L2 模式的链路结构图(状态图)如下:

- L3 模式的链路结构图(状态图)如下:

- 物理层电气部分基础(二)之 De-emphasis

- Lattice ECP3/ECP5 SerDes 简介

- 参考阅读:

- 转载链接

物理层电气部分基础(一)

之所以把物理层电气部分的文章放在链路初始化与训练文章的后面,是因为这一部分涉及到一些相关的概念,如 Beacon Signal、LTSSM 等等。

前面已经多次提及,由于本次连载的文章主要是基于 Gen2 的,所以关于 Gen3 的相关内容只会提及,但是并不会深入的介绍,如果有兴趣的可以自行阅读 Gen3 的 Spec 。

关于链路初始化与训练的文章中提到过,PCIe Spec 规定,支持新的标准的 PCIe 设备应当能够向前兼容。即 Gen2 的设备必须同时支持 2.5GT/s 和 5GT/s 。

注:当然这也不是绝对的,当每一个设备只支持 5GT/s 速率时,可以通过将 Link Capability 2 Reg 中的 Supported Link Speed 置为全 0,同时将 Link Control 2 Reg 中的 Hardware Autonomous Speed Disable 置 1 。来禁止系统尝试将速率降为 2.5GT/s 。

PCIe Spec 规定,PCIe 设备必须是 Short-Circuit Tolerant 的,这可以让 PCIe 卡支持热插拔的功能。此外,由于 PCIe 总线是一种高速的差分总线,因此,其收发两端是交流耦合的(AC-Coupled)。一般情况下,靠近发送端的链路上放置电容来滤除直流信号,如下图所示:

详细的差分收发对模型如下图所示:

当然,如果 PCIe 设备把电容集成到 Silicon(芯片)中,也是可以的(不过一般不会这么做,因为在芯片内部集成大电容成本很高)。使用交流耦合的另一个优势是,可以允许链路两端的设备使用不同的电源和地。

注:关于半导体中的电容,以及芯片周围的一堆退耦电容是什么鬼,打算找个时间单独写一篇文章来详细地聊一聊。

注:关于 PCIe 的热插拔实现机制,后续单独写一篇文章来介绍。有兴趣的读者也可自行阅读 PCIe Card Spec 的相关章节。

需要注意的是,PCIe 总线采用的是嵌入式时钟,即只有数据 Lane,并没有时钟 Lane(对于Gen1/Gen2,是通过 8b/10b 编码来嵌入和恢复时钟的;对于 Gen3 及之后的版本,是通过扰码和 128b/130b 来实现嵌入和恢复时钟的)。

L0 模式下的链路结构图(状态图)如下:

L0s 模式下的链路结构图(状态图)如下:

L1 模式下的链路结构图(状态图)如下:

L2 模式的链路结构图(状态图)如下:

L3 模式的链路结构图(状态图)如下:

物理层电气部分基础(二)之 De-emphasis

这一篇文章中,我们主要来聊一聊 PCIe 中的信号补偿技术(Signal Compensation)—— De-emphasis。需要注意的是,Gen1&Gen2 与 Gen3 的 De-emphasis 实现机制差别较大,而本文只介绍 Gen1&Gen2 相关内容。如需了解 Gen3 的相关内容,可自行查阅 Gen3 的 PCIe Spec 。

高速信号传输中有一个非常棘手的问题,就是当传输速率变得越来越高的同时,数据间隔单元(Unit Interval,UI)也会变得越来越小。这导致前一个 bit 的数据会对后面 bit 的数据造成影响,如果不去除这些影响,将会导致误码率飙升,甚至通信无法继续。

此时,还存在另一个问题,如果系统中出现几个连续的 1(或者 0 ),而接下来的信号为 0(或者 1)时,信号的电压可能达不到要求,如下图所示。这种前面的信号会影响后面的现象,我们称之为 ISI(Inter-Symbol Interference)。产生这种现象的罪魁祸首是传输线的介质损耗,具体会在 SerDes 的专栏文章中详细介绍。

注:虽然 PCIe 采用了 8b/10b 编码,但是仍然会出现连续的 5 个 0 或者 5 个 1 (一些控制字符,如 COM )。

为了解决这个问题,PCIe 采用了一种叫做 De-emphasis 的技术,具体细节如下:

-

当前后电平极性变化时,不使用 De-emphasis;

-

连续相同极性电平的第一个 bit,不使用 De-emphasis;

-

只有连续相同极性电平的第一个 bit 之后的 bit ,才使用 De-emphasis;

-

对于 2.5GT/s ,De-emphasis 将电压较少 3.5dB 。对于 5GT/s ,则是 6dB;

-

Beacon 信号也需要进行 De-emphasis,但是规则稍有差别。

注:Beacon 信号在之前关于 LTSSM 的文章中介绍过。

如下图所示:

一个 De-emphasis 的例子如下图所示:

采用 De-emphasis 之后的 PCIe 设备接收端信号如下图所示:

差分的例子:

此外,对于部分使用低摆幅(Reduced Swing)的 PCIe 设备来说,一般不需要使用 De-emphasis。考虑到,这种低摆幅的设备一般传输线都比较短(甚至是同一颗芯片/封装里面),介质损耗相对较小。

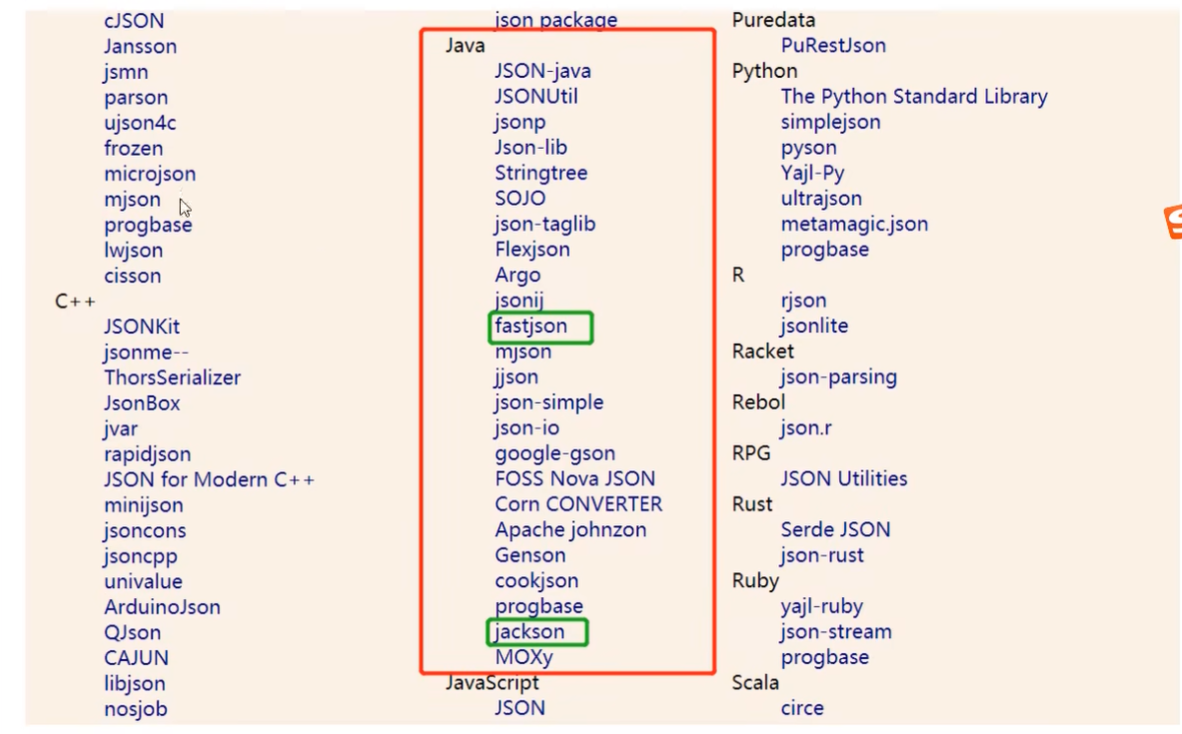

Lattice ECP3/ECP5 SerDes 简介

FPGA 发展到今天,SerDes (Serializer - Deserializer) 基本上是标配了。从 PCI 到 PCI Express,从 ATA 到 SATA,从并行 ADC 接口到 JESD204,从 RIO 到 Serial RIO,……等等,都是在借助 SerDes 来提高性能。SerDes 是非常复杂的数模混合设计,用户手册的内容只是描述了森林里面的一棵小树,并不能够解释 SerDes 是怎么工作的。而本文也主要是基于 Lattice ECP3 和 ECP5 的 SerDes UG,来简单地介绍一下 Lattice ECP3&ECP5 SerDes 的一些基本特性。如需深入了解 SerDes ,可以参考一下我之前转发的博客:SerDes 扫盲 ,以及本文附件中的硕博论文。亦或者是到 IEEE Xplore 下载相关论文资料。

废话不多说,进入正题。

Lattice 的 ECP3/ECP5 系列 FPGA 内部集成了 SerDes/PCS 的硬核(Hard Core),其速率最高可达 3.2Gbps,而 ECP5-5G 系列的 SerDes 最高可达 5Gbps。 Lattice 的 SerDes 是基于 CML 信号的,借助 PCS(物理编码子层,Physical Coding Sublayer)可以支持 PCI Express、JESD204A/B、SD-SDI、HD-SDI、3G-SDI、GbE、CPRI、Gigabit Ethernet (1GbE and SGMII) 和 XAUI 等多种串行通信协议,具体如下图所示。

就 PCIe(PCI Express)而言,ECP3/ECP5 可支持 1.0/1.1 版本(2.5Gbps),而 ECP5-5G 还可支持 2.0 版本(5Gbps)。借助 Lattice 提供的 PCIe 相关的 IP (Endpoint & Root),可以快速的完成基于 FPGA 的 PCIe 设备的开发。

Lattice ECP3,ECP5(ECP5-5G)的 SerDes/PCS 结构基本相同,区别主要在于 ECP5 将两个 SerDes/PCS 通道合并到一个叫做 DCU 的模块中去。ECP5 的每一个 DCU 均包含一个 AUX 通道(以及 TxPLL),而 ECP3 每四个 SerDes/PCS 通道才包含一个 AUX 通道。ECP3 和 ECP5 的结构图分别如下图所示:

其中,ECP5 的 SerDes/PCS 的单个通道的详细结构图如下图所示:

ECP5 的 SerDes 时钟结构图如下:

注:本文只是对 Lattice ECP3/ECP5 器件中的 SerDes/PCS 进行了简要的介绍,具体还请阅读参考阅读中的相关 UG 。

参考阅读:

-

Lattice ECP3 SerDes/PCS User Guide:

LatticeECP3SerdesPCS UsageGuide.pdf -

Lattice ECP5/ECP5-5G SerDes/PCS User Guide:

ECP5 and ECP5-5G SERDESPCS Usage Guide.pdf -

10Gbps-SerDes中的高速接口设计:

10Gbps-SerDes中的高速接口设计.pdf -

高速SERDES接口芯片设计关键技术研究:

高速SERDES接口芯片设计关键技术研究.pdf

转载链接

- 物理层电气部分基础(一)

- 物理层电气部分基础(二)之 De-emphasis

- Lattice ECP3/ECP5 SerDes 简介

☆