参考来源:《超标量处理器设计》—— 姚永斌

关于Multi-Port Cache可以参考:https://compas.cs.stonybrook.edu/~nhonarmand/courses/sp16/cse502/slides/04-caches.pdf

为了实现每个周期执行多条load/store指令,Cache必须支持多端口。

True Multi-Port

现实中不会对Cache设计真实的多端口。

因为如果真的要实现硬件电路上的多端口Cache设计,所有Cache中的控制通路和数据通路都需要复制。

也就需要两套地址解码器,两个端口可以同时独立地寻址Tag SRAM和Data SRAM。

也需要两个多路选择器(Way Mux),用来同时读取两个端口数据。

比较器的数量也要加倍,用来判断两个端口的命中情况。

也需要两个对齐器(Aligner)来完成字节或者半字节读取。

Tag SRAM和Data SRAM每个cell都需要同时支持两个并行的读取操作。

不过此方案消耗的硬件资源太大,需要驱动多个端口导致处理器周期更长,功耗更高。

所以一般不采用此类设计。

Multiple Cache Copies

复制Tag SRAM和Data SRAM,消除对处理器周期的影响。

但是会浪费较多的面积,并且需要保持两个Cache的同步,例如:

store指令需要同时写到两个Cache,当一个Cache发生了Cache Line替换,则另一个Cache copy也必须替换,保持一致。

Multi-Banking

将Cache分为多个小型的bank,每个bank中只有一个端口。

如果一个周期内,Cache多个端口访问请求位于不同bank之中,并不会引起问题。

但是如果两个或者多个端口地址位于同一个bank中,就会引起bank confict冲突。

此方法下,N端口Cache仍然需要:

N个地址解码器+N个多路选择器+N个比较器+N个对齐器。

但是Data SRAM无需多端口,提高了响应需求。

但同时由于需要判断每个端口是否命中,对于Tag SRAM还是需要多端口读取。

由于每个Cache端口请求都需要访问到bank,所以bank越多,布线资源就占用越多。

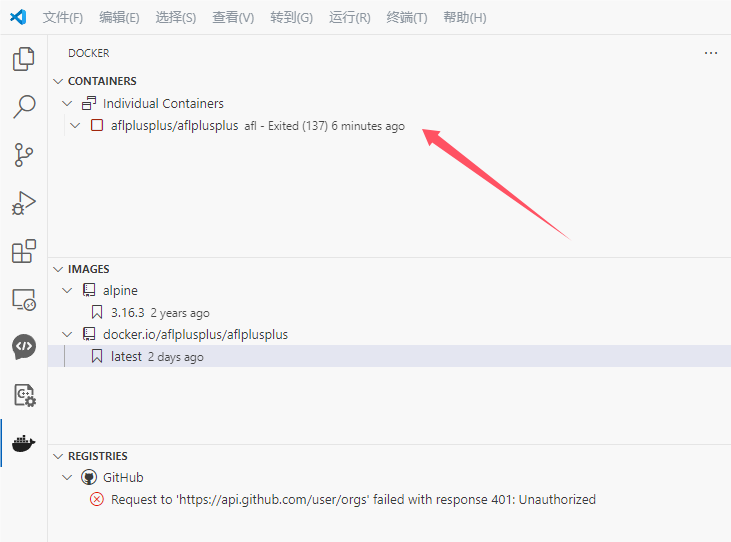

AMD Multi-Port Cache

AMD的皓龙系列是64位处理器,但是处理器的地址却是简化的设计。

它的虚拟地址是48位,物理地址为40位,从而来减少硅片面积。

处理器D-Cache则是采用了双端口,每个端口都是64位的位宽,能够在一个周期内同时运行load/store指令。

这个Cache多端口的功能就是通过Multi-Banking机制实现的,具体设计如下:

从上图可以看到,由于每个Bank都是单端口的SRAM,保证硅片面积消耗和访问速度的平衡,Bank数量减少也大大减少了冲突概率。