电路版图文件+PDK,88出,点击此处获取,24h秒发

PDF文件免费,已绑定

《集成电路版图设计课程》

课程设计(大作业)报告

2023 - 2024 学年第 1 学期

题 目 CMOS运算放大器的电路设计

专 业

班 级

学生姓名

学生学号

指导教师

日 期

课程设计(大作业)报告书写内容提纲(供参考):

一、课程设计(大作业)目的;

二、课程设计(大作业)具体要求;

三、课程设计(大作业)具体内容(含设计图纸等);

四、总结(感想或心得等);

五、指导教师评分及评语。

目录

1 CMOS运算放大器...................................... 1

1.1 电路结构分析.................................... 1

1.2 作用及应用........................................ 1

1.3 …........................................................ 1

2 CMOS运算放大器的电路设计.................. 1

2.1 …........................................................ 1

3 CMOS运算放大器的电路仿真.................. 1

3.1 直流仿真............................................ 1

3.2 交流仿真............................................ 2

4 CMOS运算放大器的版图设计.................. 1

4.1 DRS验证........................................... 1

4.2 LVS验证........................................... 1

5 总结.............................................................. 1

CMOS运算放大器

-

- 电路结构分析

根据拉扎维课本中的结构,决定采用带密勒补偿的2级OTA(消零方式为串联电阻),电路原理图如图1所示,并在Cadence618 virtuoso中采用smic18mmrf工艺库进行原理图的搭建并进行仿真。

图1 运放结构框图

M2、M3和M4管共同构成电流镜提供偏置;M0和M1为差分输入对管用来消除共模干扰;M5和M6提供有源电流镜负载,将差分输入转为单端输出,M8为第二级输入管,也是输出管。由于采用了两级放大,为双极点系统,需要采用密勒补偿电容来提高稳定性。

-

- 作用及应用

运算放大器常常被用在反馈系统中,进而实现丰富多彩的功能,例如I-V转换和仪表测量等。实际的运放产品却不可能达到理想运放一样的零输入失调电压,零输出阻抗,无穷大开环增益等性能,而且某些参数指标被证明是冲突的,这需要设计人员对此进行折衷。在这些参数指标中,运算放大器的开环增益在许多应用场合中,尤其是高精度应用中会带来严重的误差,甚至导致运放无法正常使用,因此提高开环增益是十分有必要的,本文采用两级放大来提高开环增益。另外,在某些领域要求运算放大器的输出电压能够接近轨到轨输出电压范围。因此本文采用了电流源做负载的共源极放大器作为第二级,其输出摆幅接近于轨对轨。

- CMOS运算放大器的电路设计

由图1所得,M4、M2和M3为普通电流镜,用于为输入差分对和输出管提供尾电流。在尺寸的设计上,W值一般没有什么要求,保证VDSAT足够低,能通过所需要的电流即可,L值需要着重考虑。一般电流镜的L会统一取1u或者2u,L值增大可以显著的降低沟长调制效应,因为饱和区的电流公式为

ID=1/2 unCox W/L (VGS-VTH)2(1+λVDS)

其中,λ值则和器件的L成反比,所以L越大越好,但L过大又会影响MOS器件的电流能力,以及在做负载时,面积过大会引入额外的次极点,从而降低稳定性。所以在本设计中NMOS的L值统一取1u,PMOS的L值统一取2u。

第一级放大器为有源电流镜做负载的共源极差分对,其中M0和M1为输入管,第一级放大器的增益为

AV1=gm1(roN||roP)

其中roN||roP为第一级输出端看进去的阻抗,对于MOS管的ro=1/(λID),所以提高增益的方法之一就是通过提高器件的L值,但和上述讨论过的一样,增大L值会造成稳定性的降低。而gm1又和电流尺寸成正比,gm1=(2ID unCox W/L)1/2,所以在设计中我们一般会将输入管的尺寸做的比较大,其M=10。

由于第一级为单端输出,第二级就为电流源做负载的单级共源极放大器,其增益表达式和第一级相同为

AV2=gm3(ro3||ro8)

所以整体的增益就是AV1*AV2。和第一极相同,输出管M3的尺寸和电流在设计中会给较大值,从而显著提升增益。

下面进行稳定性的分析,对于未采用补偿技术的2级OTA,其是一个两极点系统,而两极点系统是必然震荡的。所以需要采用密勒补偿C0俩来进行极点的分离,将主极点的频率进一步降低,而次极点则推向带外,其和GBW的关系一般为2-3倍,为保证PM大于60°。由于电容C0引入了一条前馈通路,会引进右零点,这个右零点会恶化稳定性,由于缓冲器会消耗额外的功耗与面积,一般会采用零位电阻引入一个左极点来抵消右零点。

对于采用密勒补偿后的2级OTA,其GBW=gm1/C0,次极点=gm3/CL。在设计中会合理调节C0和R0的值,从而使得GBW和PM达到最佳性能。

2级OTA的压摆率(瞬态响应)SR=ISS/C0,其指在输入端存在大的阶跃信号下,尾管电流会流向一边的输入管,从而对密勒电容充电,其和GWB一样,速度过快,也会意味着PM的降低,需要通过提高整体的功耗来得到更高的SR。

给出本设计所采用的尺寸,总结如下表

| 器件 | 参数 | 器件 | 参数 |

| M0 | 20u/1u(M=10) | M5 | 40u/0.5u(M=1) |

| M1 | 20u/1u(M=10) | M6 | 40u/0.5u(M=1) |

| M2 | 20u/1u(M=5) | M7 | 40u/0.5u(M=10) |

| M3 | 20u/1u(M=10) | C0 | 2.5pF |

| M4 | 20u/1u(M=1) | R0 | 380 |

并给出本二级OTA的设计指标如下表:

| 参数 | 数值 |

| AV | 80dB |

| GBW | 300M |

| PM | 60° |

| CMRR | 70dB |

| PSRR | 70dB |

| SR | 300V/us |

| IQ | 5mA |

- CMOS运算放大器的电路仿真

如下图为运放的仿真电路图,因为运放在使用中都是接成单位增益负反馈来验证其各种性能指标,其中I12为理想电流源,V0用于提供3.3V的电源(因为采用的器件均为n33、p33),V1用于提供DC电平,V2英用于提供斜波信号验证压摆率SR,V4用于STB仿真环路,CL=1pF。

图2 仿真电路图

-

- 直流仿真

进行一切仿真的前提,是进行DC仿真,如下图3所示,可以看到所有管子均工作在饱和区,输入为1.6V,输出跟随输入也为1.6013V,不相等是因为2级OTA的开环增益没有无穷大,所以会存在系统失调电压。所以本电路功能正常。

图3 DC工作点

-

- 交流仿真

为验证带宽和稳定性,进行stb仿真得到仿真图如下图4,可以看到开环增益AV=85dB,GBW=344.7MHz,PM=64°。由于采用了2级放大,并且面积和电流均比较大,所以增益可以做到很高,有85dB,而整体运放的功耗也比较大,可以在GBW比较大的同时,还保持稳定。

图4开环频率特性

进行AC仿真,首先个2个输入端加交流小信号,进行CMRR仿真得下图为77dB。CMRR为输出端对于共模输入电平的抑制能力。

图5 CMRR

进行AC仿真,在电源端加交流小信号,进行PSRR仿真得下图为86.4dB。PSRR为输出端对于电源电压波动的抑制能力。

图6 PSRR

-

- 瞬态仿真

进行瞬态仿真,输入给0.2-3V的方波信号,得到输入输出波形图如下,可以得到SR=324V/us,其中建立时间为11us左右。

图7 SR

在TRAN下进行静态电流的仿真,得到IQ=2.24mA。由于GBW和SR均比较大,所以静态电流同样比较大。

图8 功耗

最后对所有仿真参数进行总结得到下表:

| 参数 | 数值 |

| AV | 85dB |

| GBW | 344M |

| PM | 64° |

| CMRR | 77dB |

| PSRR | 86dB |

| SR | 324V/us |

| IQ | 2.24mA |

所有参数均满足设计时的指标要求。

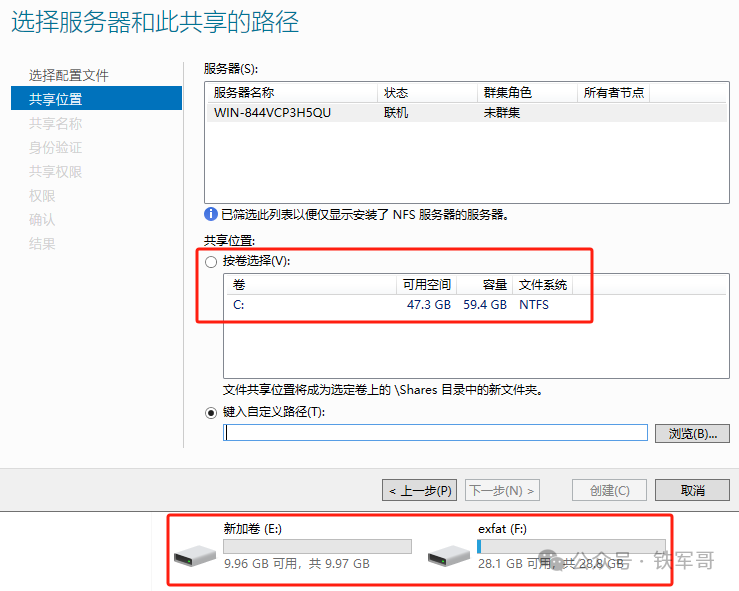

- CMOS运算放大器的版图设计

- DRC验证

- LVS验证

- 总结

在2级运放的设计中,AV、GBW、PM以及SR和功耗是相互制衡的参数,GBW过大意味着比较好的动态性能,但稳定性肯定会变差,AV过大意味着过大的尺寸和电流,需要耗费更多的面积和功耗。所以一般在设计中,会优先根据开环增益来选择结构,高增益除过两级放大,还需要采用cascode等技术进一步提升增益,而GBW和SR的大小,则决定了本电路的功耗需要取多大,例如本文中的GBW和SR均在300以上,如果将总的电流做到1mA以内,即便通过降低密勒补偿电容C0可以得到响应的指标,但PM肯定会特别差。所以在设计中一定要注意各个参数的相互权衡制约关系。

|

《集成电路版图设计课程》

课程设计(大作业)报告

2023 - 2024 学年第 1 学期

题 目 CMOS运算放大器的电路设计

专 业

班 级

学生姓名

学生学号

指导教师

日 期

课程设计(大作业)报告书写内容提纲(供参考):

一、课程设计(大作业)目的;

二、课程设计(大作业)具体要求;

三、课程设计(大作业)具体内容(含设计图纸等);

四、总结(感想或心得等);

五、指导教师评分及评语。

目录

1 CMOS运算放大器...................................... 1

1.1 电路结构分析.................................... 1

1.2 作用及应用........................................ 1

1.3 …........................................................ 1

2 CMOS运算放大器的电路设计.................. 1

2.1 …........................................................ 1

3 CMOS运算放大器的电路仿真.................. 1

3.1 直流仿真............................................ 1

3.2 交流仿真............................................ 2

4 CMOS运算放大器的版图设计.................. 1

4.1 DRS验证........................................... 1

4.2 LVS验证........................................... 1

5 总结.............................................................. 1

CMOS运算放大器

-

- 电路结构分析

根据拉扎维课本中的结构,决定采用带密勒补偿的2级OTA(消零方式为串联电阻),电路原理图如图1所示,并在Cadence618 virtuoso中采用smic18mmrf工艺库进行原理图的搭建并进行仿真。

图1 运放结构框图

M2、M3和M4管共同构成电流镜提供偏置;M0和M1为差分输入对管用来消除共模干扰;M5和M6提供有源电流镜负载,将差分输入转为单端输出,M8为第二级输入管,也是输出管。由于采用了两级放大,为双极点系统,需要采用密勒补偿电容来提高稳定性。

-

- 作用及应用

运算放大器常常被用在反馈系统中,进而实现丰富多彩的功能,例如I-V转换和仪表测量等。实际的运放产品却不可能达到理想运放一样的零输入失调电压,零输出阻抗,无穷大开环增益等性能,而且某些参数指标被证明是冲突的,这需要设计人员对此进行折衷。在这些参数指标中,运算放大器的开环增益在许多应用场合中,尤其是高精度应用中会带来严重的误差,甚至导致运放无法正常使用,因此提高开环增益是十分有必要的,本文采用两级放大来提高开环增益。另外,在某些领域要求运算放大器的输出电压能够接近轨到轨输出电压范围。因此本文采用了电流源做负载的共源极放大器作为第二级,其输出摆幅接近于轨对轨。

- CMOS运算放大器的电路设计

由图1所得,M4、M2和M3为普通电流镜,用于为输入差分对和输出管提供尾电流。在尺寸的设计上,W值一般没有什么要求,保证VDSAT足够低,能通过所需要的电流即可,L值需要着重考虑。一般电流镜的L会统一取1u或者2u,L值增大可以显著的降低沟长调制效应,因为饱和区的电流公式为

ID=1/2 unCox W/L (VGS-VTH)2(1+λVDS)

其中,λ值则和器件的L成反比,所以L越大越好,但L过大又会影响MOS器件的电流能力,以及在做负载时,面积过大会引入额外的次极点,从而降低稳定性。所以在本设计中NMOS的L值统一取1u,PMOS的L值统一取2u。

第一级放大器为有源电流镜做负载的共源极差分对,其中M0和M1为输入管,第一级放大器的增益为

AV1=gm1(roN||roP)

其中roN||roP为第一级输出端看进去的阻抗,对于MOS管的ro=1/(λID),所以提高增益的方法之一就是通过提高器件的L值,但和上述讨论过的一样,增大L值会造成稳定性的降低。而gm1又和电流尺寸成正比,gm1=(2ID unCox W/L)1/2,所以在设计中我们一般会将输入管的尺寸做的比较大,其M=10。

由于第一级为单端输出,第二级就为电流源做负载的单级共源极放大器,其增益表达式和第一级相同为

AV2=gm3(ro3||ro8)

所以整体的增益就是AV1*AV2。和第一极相同,输出管M3的尺寸和电流在设计中会给较大值,从而显著提升增益。

下面进行稳定性的分析,对于未采用补偿技术的2级OTA,其是一个两极点系统,而两极点系统是必然震荡的。所以需要采用密勒补偿C0俩来进行极点的分离,将主极点的频率进一步降低,而次极点则推向带外,其和GBW的关系一般为2-3倍,为保证PM大于60°。由于电容C0引入了一条前馈通路,会引进右零点,这个右零点会恶化稳定性,由于缓冲器会消耗额外的功耗与面积,一般会采用零位电阻引入一个左极点来抵消右零点。

对于采用密勒补偿后的2级OTA,其GBW=gm1/C0,次极点=gm3/CL。在设计中会合理调节C0和R0的值,从而使得GBW和PM达到最佳性能。

2级OTA的压摆率(瞬态响应)SR=ISS/C0,其指在输入端存在大的阶跃信号下,尾管电流会流向一边的输入管,从而对密勒电容充电,其和GWB一样,速度过快,也会意味着PM的降低,需要通过提高整体的功耗来得到更高的SR。

给出本设计所采用的尺寸,总结如下表

| 器件 | 参数 | 器件 | 参数 |

| M0 | 20u/1u(M=10) | M5 | 40u/0.5u(M=1) |

| M1 | 20u/1u(M=10) | M6 | 40u/0.5u(M=1) |

| M2 | 20u/1u(M=5) | M7 | 40u/0.5u(M=10) |

| M3 | 20u/1u(M=10) | C0 | 2.5pF |

| M4 | 20u/1u(M=1) | R0 | 380 |

并给出本二级OTA的设计指标如下表:

| 参数 | 数值 |

| AV | 80dB |

| GBW | 300M |

| PM | 60° |

| CMRR | 70dB |

| PSRR | 70dB |

| SR | 300V/us |

| IQ | 5mA |

- CMOS运算放大器的电路仿真

如下图为运放的仿真电路图,因为运放在使用中都是接成单位增益负反馈来验证其各种性能指标,其中I12为理想电流源,V0用于提供3.3V的电源(因为采用的器件均为n33、p33),V1用于提供DC电平,V2英用于提供斜波信号验证压摆率SR,V4用于STB仿真环路,CL=1pF。

图2 仿真电路图

-

- 直流仿真

进行一切仿真的前提,是进行DC仿真,如下图3所示,可以看到所有管子均工作在饱和区,输入为1.6V,输出跟随输入也为1.6013V,不相等是因为2级OTA的开环增益没有无穷大,所以会存在系统失调电压。所以本电路功能正常。

图3 DC工作点

-

- 交流仿真

为验证带宽和稳定性,进行stb仿真得到仿真图如下图4,可以看到开环增益AV=85dB,GBW=344.7MHz,PM=64°。由于采用了2级放大,并且面积和电流均比较大,所以增益可以做到很高,有85dB,而整体运放的功耗也比较大,可以在GBW比较大的同时,还保持稳定。

图4开环频率特性

进行AC仿真,首先个2个输入端加交流小信号,进行CMRR仿真得下图为77dB。CMRR为输出端对于共模输入电平的抑制能力。

图5 CMRR

进行AC仿真,在电源端加交流小信号,进行PSRR仿真得下图为86.4dB。PSRR为输出端对于电源电压波动的抑制能力。

图6 PSRR

-

- 瞬态仿真

进行瞬态仿真,输入给0.2-3V的方波信号,得到输入输出波形图如下,可以得到SR=324V/us,其中建立时间为11us左右。

图7 SR

在TRAN下进行静态电流的仿真,得到IQ=2.24mA。由于GBW和SR均比较大,所以静态电流同样比较大。

图8 功耗

最后对所有仿真参数进行总结得到下表:

| 参数 | 数值 |

| AV | 85dB |

| GBW | 344M |

| PM | 64° |

| CMRR | 77dB |

| PSRR | 86dB |

| SR | 324V/us |

| IQ | 2.24mA |

所有参数均满足设计时的指标要求。

- CMOS运算放大器的版图设计

- DRC验证

- LVS验证

- 总结

在2级运放的设计中,AV、GBW、PM以及SR和功耗是相互制衡的参数,GBW过大意味着比较好的动态性能,但稳定性肯定会变差,AV过大意味着过大的尺寸和电流,需要耗费更多的面积和功耗。所以一般在设计中,会优先根据开环增益来选择结构,高增益除过两级放大,还需要采用cascode等技术进一步提升增益,而GBW和SR的大小,则决定了本电路的功耗需要取多大,例如本文中的GBW和SR均在300以上,如果将总的电流做到1mA以内,即便通过降低密勒补偿电容C0可以得到响应的指标,但PM肯定会特别差。所以在设计中一定要注意各个参数的相互权衡制约关系。

![【力扣热题100】[Java版] 刷题笔记-104. 二叉树的最大深度](https://i-blog.csdnimg.cn/direct/fe6e3b287d2f46d791b6935a41210914.png)