【网络原理】UDP协议

目录

一. UDP 报文格式

(1)端口号

(2)UDP长度

(3)校验和

UDP协议属于传输层协议,由操作系统内核内置

一. UDP 报文格式

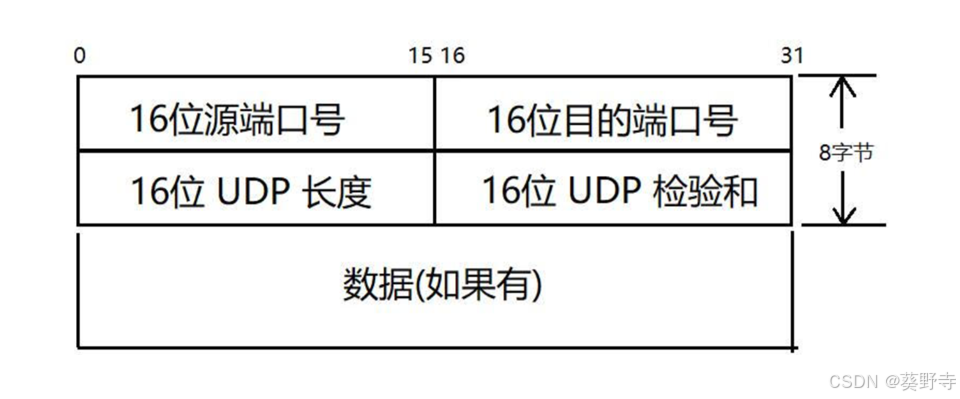

UDP数据报:无连接,不可靠传输,面向数据报,全双工

在UDP报头中,总共由4个字段,每个字段2个字节(一共8个字节)

(1)端口号

- IP地址确定主机的地址 ,端口号确定主机应用程序

- 在协议报头中使用2个字节表示端口号,端口号的取值范围是0-65535

- 端口号全0表示无意义

(2)UDP长度

- 一个UDP数据报的最大长度是64KB,具体大小是64KB-8B

- 最小长度是8B

- 如果数据报的长度超过64KB,那么可能会出现数据截断现象,后面的数据获取不到

在我们生活中,一张图片的大小都可能是几MB,UDP只有64KB,UDP的空间完全不够,我们的日常使用,如果将UDP的长度修改变大,确实可以解决空间不够问题,但是如果修改UDP格式,那么全世界使用UDP的程序,都需要进行改变,否则不兼容(想法很美好,实现很困难)

(3)校验和

校验和:验证接收方,接收的数据是否正确

数据在网络传输的过程中,依靠光/电信号/电磁波进行传输,很容易受到外界的干扰,经过一个磁场高的地方,可能会把原来的低频信号转变成了高频信号(0->1),这种现象叫做比特翻转,也有可能会发生信号缺失的情况

校验和的作用:识别当前的数据是否出现了比特翻转,是不是正确的数据,如果不是正确的数据,就会直接把这个错误的数据扔掉

CRC算法 (循环冗余算法

CRC算法:将数据视为二进制多项式,除以预定义的生成多项式,余数作为校验值。

- 发送方,在发送数据之前,根据CRC算法,计算一遍CRC值,将CRC值放入UDP数据报中,一起发送出去

- 接收方,在收到数据之后,根据同样的算法,再计算一遍CRC值,将得到的值和发送方保存的CRC值进行对比,如果数据不同,则表示传输的数据有问题,反之,则正常

注意:如果数据相同,也有可能存在问题,如果两个比特位,同时发生了比特翻转,导致最后得到的结果一样,那么这种方法就不能判断数据的正确性(可能性很小)

我们可以使用更高精度的校验算法(md5/sha1算法),就不怕出现上述问题

md5算法

md5算法,具体的数学公式很复杂 ,不像CRC算法那么简单,具有以下特征

(1) 定长

- 无论数据有多长,最后得出来的结果始终都是固定长度

- 常见的长度有16位版本和32位版本

(2)分散

- md5算法,只要原始数据改变一点点,最后得到的结果差异会非常大

(3)不可逆

- md5算法,给你一个结果,你是无法得到原始数据

- 如果非要得到这个结果,只能使用暴力枚举的方法得到原始数据

点赞的宝子今晚自动触发「躺赢锦鲤」buff!