实验目的

- 掌握使用Vivado软件进行设计、综合、仿真、布线的方法。

- 掌握FPGA程序的下载方法。

- 掌握使用Verilog HDL设计分频器的方法。

实验要求

采用Verilog HDL语言设计分频器,实现以下功能:

- 输出时钟周期为1s的分频时钟信号;

- 通过LED灯或数码管显示秒数,可对9s内的秒数进行计数;

- 当按下复位按键时,重新开始计数。

对设计进行综合、仿真、布线、下载和测试。

实验过程

- 打开Vivado软件,新建一个工程。

- 新建设计文件,使用Verilog HDL语言设计程序,实现分频器功能。

代码如下:

我这个是通过一个数码管显示的

timescale 1ns / 1ps

module exp2(input clk,//时钟input rst,//复位output reg clk_out,//分频后output reg [7:0]out,//数码管位选和显示

);

parameter LW = 25000000;reg [31:0]count;

reg [3:0]second;

always @(posedge clk or negedge rst) beginif(!rst)begin clk_out <= 0;count <= 0;endelseif (count < LW - 1)begincount <= count + 1;endelsebegincount <= 0;clk_out <= ~clk_out;endend

always @(negedge clk_out or negedge rst)

beginif (!rst)second <= 0;elseif (second < 9)second <= second + 1;elsesecond <= 0;case(second)0:out <= 8'b01111110;1:out <= 8'b00110000;2:out <= 8'b01101101;3:out <= 8'b01111001;4:out <= 8'b00110011;5:out <= 8'b01011011;6:out <= 8'b01011111;7:out <= 8'b01110000;8:out <= 8'b01111111;9:out <= 8'b01111011;default: out <= 0;endcase;

end

endmodule

仿真代码如下:

`timescale 1ns / 1psmodule exp2_t;reg clk;reg rst;always #10 clk=~clk;wire [7:0]out;wire clk_out;exp2 exptest(.clk(clk),.rst(rst),.clk_out(clk_out),.out(out));

initialbeginclk=0;rst=0;#4000rst=1;endendmodule

实验结果

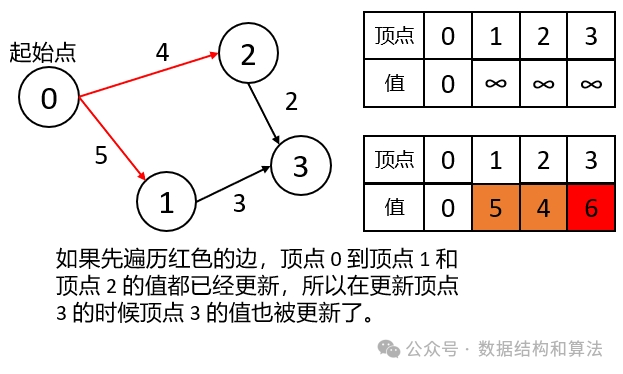

总结

本次实验中,将always块中的敏感事件写错了,经过仿真结果找出问题;在秒表计数的if-else语句中将计数的变量搞错,导致不能正确的实现秒表过一秒加一的操作,通过本次实验,我不仅掌握了使用Vivado软件进行综合、仿真、布线、下载和测试的方法,也加强了对Verilog HDL语言的掌握和应用能力。