PCI 总线最早采用的中断机制是 INTx,这是基于边带信号的。后续的 PCI/PCI-X版本,为了消除边带信号,降低系统的硬件设计复杂度,逐渐采用了 MSI(Message Signaled Interrupt)/MSI-X(消息信号中断)的中断机制。

MSI/MSI-X 与 PCIe总线中的消息(Message)的概念完全不同! MSI/MSI-X 本质上是一种 Posted Memory Write TLP。

MSI最大支持32个中断向量,MSI-X在 3.0 版本引入,对 MSI 做出了一些升级和改进,最大支持2048个中断向量。

当EP支持MSI/MSI-X时,RC可在枚举阶段对MSI/MSI-X的能力寄存器做相关配置

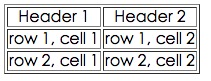

MSI能力寄存器

MSI的Capability ID = 0x05,DW1为发起中断MEM_WR TLP的地址,DW2的[15:0]为写数据,其中低bit位为对应的中断向量号。

Mask Bits的某一个位置1,则表明对应的中断向量号触发中断时,不会实际发送MEM_WR TLP;但是此时Pending Btis对应位会置1;

软件此时只能通过Polling Pending Bits来得知EP端是否有中断;如果Mask Bits的某一位置0,此时Pending Btis对应位为1,则会触发MEM_WR TLP的中断,然后硬件再clear对应的Pending Btis。

Pending Btis对于HOST是只读的。

根据地址,分为32-bit和64-bit两种格式:

Message Control格式如下:

[0:0] : MSI使能

[3:1] : EP端可支持的向量数目

[6:4] : 实际软件使能的向量数目

[7:7] : 是否是64-bit格式

[8:8] 是否支持中断mask功能

所以启用MSI功能之前,需要配置如下寄存器:

注意32-bit相比64-bit少配置一个寄存器,32-bit不支持中断mask功能时,只需配置前三个寄存器。

所以枚举设备时,驱动软件会判断EP是否支持MSI功能,并配置对应的MSI地址和数据。

MSI-X能力寄存器

MSI-X的Capability ID = 0x11,Message Control [10:0] 表示支持的中断数目,[14]为总的mask开关,[15]为使能开关

Table BIR 表示 MSI-X Table处于哪个BAR上;PBA BIR表示 PBA处于哪个BAR上;

MSI-X Table Offset为相对于BAR地址MSI-X Table的偏移地址,对于HOST是只读的

PBA Offset为为相对于BAR地址PBA的偏移地址,对于HOST是只读的

因为MSI-X最大支持2048个中断向量,并且中断地址和数据都是可配置的,像MSI那样通过寄存器来实现不太现实;所以MSI-X会分配一段ram空间存放这些信息;本系列中,将MSI-X Table映射在BAR1空间上,相对于BAR1的偏移地址在MSI-X能力寄存器中定义。

每个中断向量为一个Entry,驱动软件可配置每个Entry的地址和数据,DW3 [0:0]为该Entry的mask;

和MSI类似,也有对应的Penging Btis;每一个Penging Btis可覆盖64个中断Entry。

所以启用MSI-X功能之前,需要配置如下寄存器以及BAR1空间上的MSI-X Table

枚举阶段配置完MSI/MSI-X能力寄存器后,EP端的应用可触发MSI/MSI-X中断,两者方式有所不同:

触发MSI中断

MSI中断提供了专门的MSI相关的信号,用户在集成PCIE Controller时,可将响应信号集成到MSIC模块中。相关信号如下:

逻辑实现如下:

依次触发终端号为’hc,'h16,'hb,'ha,'h19 :

Controller接收中断后,生成相应的MEM_WR TLP,写地址为MSI能力寄存器中配置的Message Address,写数据为Message Data和中断向

量号的组合

触发MSI-X中断

MSI-X中断通过DBI写MSI-X Doorbell Register实现,DOORBELL寄存器如下:

利用DBI接口向DOORBELL地址’h948写中断向量号 'h16,'h1b,'h9,'h15,'h6

Controller依据DOORBELL配置,生成相应的MEM_WR TLP,写地址为MSI-X对应Entry中断号的Message Address,写数据为Message Data

TB中对于如何抓取VIP侧接收的MEM_WR TLP是否符合预期,可以重写callback function post_tlp_framed_in_get 或者使用received_tlp_observed_port。